Home Search Collections Journals About Contact us My IOPscience

Smart integration of silicon nanowire arrays in all-silicon thermoelectric micro-nanogenerators

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2016 Semicond. Sci. Technol. 31 084001

(http://iopscience.iop.org/0268-1242/31/8/084001)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 149.132.99.99

This content was downloaded on 05/08/2016 at 10:16

Please note that terms and conditions apply.

Semicond. Sci. Technol. 31 (2016) 084001 (11pp)

doi:10.1088/0268-1242/31/8/084001

# Smart integration of silicon nanowire arrays in all-silicon thermoelectric micro-nanogenerators

Luis Fonseca<sup>1,5</sup>, Jose-Domingo Santos<sup>2</sup>, Alberto Roncaglia<sup>3</sup>, Dario Narducci<sup>4</sup>, Carlos Calaza<sup>1</sup>, Marc Salleras<sup>1</sup>, Inci Donmez<sup>1</sup>, Albert Tarancon<sup>2</sup>, Alex Morata<sup>2</sup>, Gerard Gadea<sup>2</sup>, Luca Belsito<sup>3</sup> and Laura Zulian<sup>4</sup>

E-mail: luis.fonseca@imb-cnm.csic.es

Received 30 January 2016, revised 23 May 2016 Accepted for publication 7 June 2016 Published 30 June 2016

#### **Abstract**

Micro and nanotechnologies are called to play a key role in the fabrication of small and low cost sensors with excellent performance enabling new continuous monitoring scenarios and distributed intelligence paradigms (*Internet of Things, Trillion Sensors*). Harvesting devices providing energy autonomy to those large numbers of microsensors will be essential. In those scenarios where waste heat sources are present, thermoelectricity will be the obvious choice. However, miniaturization of state of the art thermoelectric modules is not easy with the current technologies used for their fabrication. Micro and nanotechnologies offer an interesting alternative considering that silicon in nanowire form is a material with a promising thermoelectric figure of merit. This paper presents two approaches for the integration of large numbers of silicon nanowires in a cost-effective and practical way using only micromachining and thin-film processes compatible with silicon technologies. Both approaches lead to automated physical and electrical integration of medium-high density stacked arrays of crystalline or polycrystalline silicon nanowires with arbitrary length (tens to hundreds microns) and diameters below 100 nm.

Keywords: silicon nanowires, silicon technologies, thermoelectricity, top-down approach, bottom-up approach

1

(Some figures may appear in colour only in the online journal)

#### Introduction

In order to fulfill new paradigms such as *Internet of Things* or *Trillion Sensors* large volume fabrication of miniaturized

Original content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

devices needs to be addressed. In order to provide those devices with energy autonomy, solutions other than primary batteries are advisable, i.e. energy harvesting approaches. In those application scenarios where residual heat is present thermoelectricity may be exploited as a source of energy autonomy. Miniaturization and large volume fabrication are significant characteristics of silicon technologies and, indeed, many sensors and auxiliary electronic and communication devices are fabricated with such technologies. On the other hand, the assembly technology used in standard thermoelectric modules is not prone to automation and

<sup>&</sup>lt;sup>1</sup> IMB-CNM (CSIC), Campus UAB, E-08193 Bellaterra, Spain

<sup>&</sup>lt;sup>2</sup> IREC, Jardí de les Dones de Negre 1, E-08930 Sant Adrià de Besòs, Spain

<sup>&</sup>lt;sup>3</sup> CNR-IMM, V.Piero Gobetti, 101, I-40129 Bologna, Italy

<sup>&</sup>lt;sup>4</sup>Dept. Materials Science, University of Milano Bicocca, v. R. Cozzi 55, I-20125 Milan, Italy

<sup>&</sup>lt;sup>5</sup> Author to whom any correspondence should be addressed.

miniaturization and usually needs materials with complex internal structure involving scarce elements.

Up to ten years ago silicon was considered a material of poor interest for thermoelectric purposes. Although silicon is an abundant inexpensive material and a fantastic technology is available for its processing, its thermoelectric figure of merit ZT is too low compared to that of standard thermoelectric materials to make it interesting in the field of thermoelectric generation. This opinion abruptly changed with the discovery that thermal conductivity in silicon nanowires (Si NWs) decreases significantly when the wire diameter is brought to nanometer scale. In two seminal papers appeared in 2008 [1, 2], two collaborations independently showed that Si thermal conductivity decreases by a factor of 20 when moving from bulk silicon to nanowires (for which  $\kappa \approx$  $6 \text{ W m}^{-1} \text{ K}^{-1}$  at 300 K), provided that the surface roughness is such to enable specular reflection of electrons while incoherently scattering phonons. This brought ZT of single crystalline silicon NWs to a region, around 0.6, for which applications are of interest. Although the detailed mechanism of selective scattering of phonons over electrons was not completely clear in 2008, it was however evident that two critical sizes ruled  $\kappa$ , namely the NW diameter and the NW surface roughness  $\sigma$ . Actually, in any nanostructure (either 1D or 2D) phonon mean free path  $\Lambda$  is limited by scattering at outer surfaces, provided that phonon wavelength  $\lambda$  is small compared to  $\sigma$ . This interplay between  $\lambda$  and  $\sigma$  was actually well known in nanolayers: no damping of  $\kappa$  had been observed in multilayers obtained by MBE, where sharp interfaces cause phonons to be coherently scattered (reflected) with no reduction of their  $\Lambda$ , while a dramatic reduction of the thermal conductivity was reported to occur in ultrathin films with ruggedized outer surfaces [3].

The enhanced properties of silicon NWs have been proved by painstakingly placing a single nanowire (grown elsewhere and sonicated) in a suspended ad hoc thermal test microstructure and securing its mechanical and electrical bonds by means of FIB-assisted processes such as in [1]. It is obvious that fabricating a useful thermoelectric device will demand much more populated arrays of Si NWs and they need to be integrated in a way that their connections to the thermally active parts of the generator are achieved in an automated way. Monolithic silicon top-down approaches have been already assayed to achieve this goal with silicon technologies. For instance, a planar micro thermo-electric generator (TEG) can be obtained by fabricating a suspended silicon platform and defining a low density flat Si NWs array in a silicon-on-insulator (SOI) wafer with a nano-thick device layer [2]. The resulting devices are fragile and require the use of time-consuming nanopatterning techniques such as e-beam or FIB. A second approach is using state of the art submicron CMOS technologies to obtain more robust structures and higher density arrays of Si NWs. In this case the microgenerator is of vertical architecture, which adapts better to naturally occurring thermal gradients, but the 'height' of the vertically defined nanowires is limited to the order of one micron, which is not large enough to develop significant temperature differences across them [4].

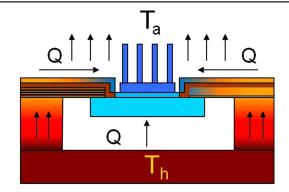

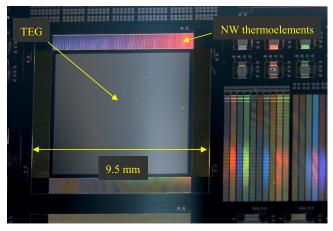

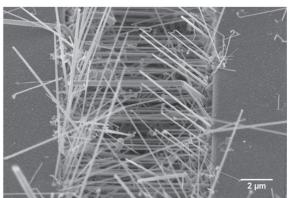

Figure 1. Lateral micro-TEG based on Si NWs integrated in a micromachined device.

In this work, two alternative approaches for the automatic integration of a large number of several tens of microns long Si NWs into lateral thermoelectric devices are introduced. The focus is put on integration feasibility, device architecture and compatible processing sequence definition, in order to bring the previously reported good thermoelectric features of single Si NWs a step forward towards useful devices. Both single-crystalline and polycrystalline silicon NWs are considered. Actually, grain boundaries are known to have additional beneficial effects on the reduction of NW thermal conductivity [5]. This evidence is in good agreement with recent analyses by Yang and Dames [6]. The reduction of  $\kappa$  in nanostructures is the result of the selective suppression of phonon modes. Nano-objects of appropriate size and spacing inhibit heat conduction by phonons with  $\lambda$  smaller than the scatterer size and  $\Lambda$  comparable or larger than their spacing. Thus, nano-grains by at least one order of magnitude smaller than the diameter of the NWs will suppress phonon modes with wavelengths larger than surface roughness  $\sigma$ , which are not affected by the incoherent scattering at the nanostructure outer walls. As a result, thermal conductivities of 3 -4 W m<sup>-1</sup> K<sup>-1</sup> were measured in poly-Si NWs with diameters around 100 nm, namely  $\kappa$  values by a factor 2 smaller than in single-crystalline Si NWs of similar size [6]. Consistently, a much less evident effect was reported in poly-Si nanolayers as in that case the grain size was comparable to the nanolayer thickness [7]. On the other hand, the presence of grain boundaries affects negatively the NW power factor (electric conductivity is reduced). In spite of this trade-off, values of  $ZT \approx 0.1$  were obtained at 300 K [8], which justifies further investigation of poly-Si NWs and the effort of devising an approach for their mass integration.

# Integration of Si NWs into silicon planar architectures

For both single crystalline and polycrystalline Si NWs, the architectural approach considered in this work is planar in order to make their integration consistent with typical silicon technologies. Transposing natural vertical thermal gradients into a lateral architecture requires the definition of a thermally isolated platform to properly re-steer heat flow. The typical resulting

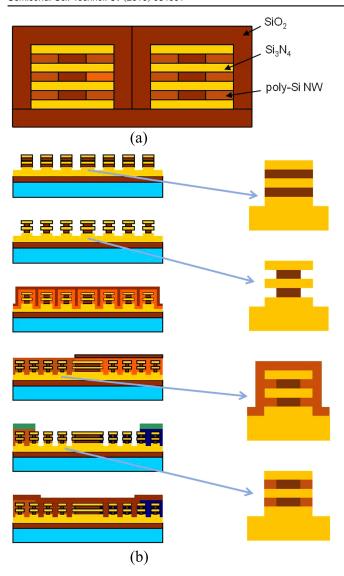

**Figure 2.** Top-down fabricated polycrystalline Si NWs multilayered arrays for micro-TEGs. (a) Schematic cross-section of the stacked NWs arrays. (b) Critical sequence of main steps leading to n and p poly-Si NWs embedded in a Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> structured multilayer.

geometry is depicted in figure 1 where a lateral temperature difference is obtained from a vertical gradient using a structure consisting of a suspended platform (usually in contact with a heater exchanger) connected via Si NWs with the surrounding silicon bulk rim (usually in contact with the heat source). Such suspended platforms can be routinely obtained by standard silicon micromachining. In this way, the use of silicon device-making technologies together with the use of monolithically integrated Si NWs as thermoelectric material pave the way to all-silicon thermoelectric micro-nanogenerators.

#### Top-down integration of poly-Si NWs arrays

The first approach considered in this work provides a way to integrate medium-high densities of stacked top-down

a

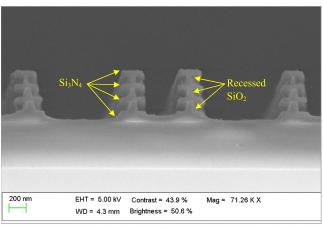

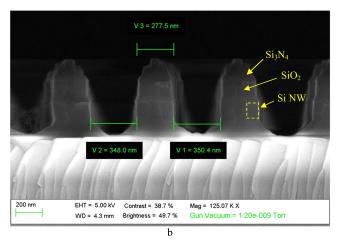

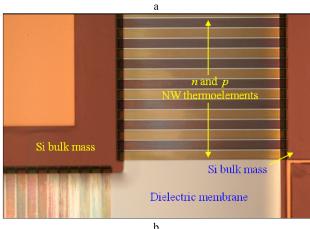

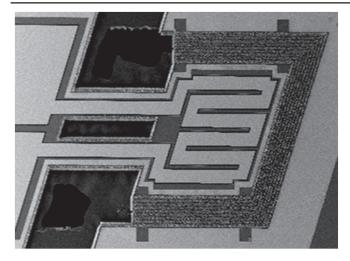

Figure 3. (a)  $\rm Si_3N_4/SiO_2$  nanotemplates and (b) high-density multilayered embedded poly-Si NWs.

polysilicon nanowires. It makes use of multilayered strips of very thin silicon oxide and silicon nitride films vertically patterned [9]. A selective silicon oxide wet etch is performed to produce lateral nano-recesses in the oxide layers of the stacked structure. A conformal polysilicon deposition and dry etch-back follows, leaving behind polysilicon filled nano-recesses that give rise to arrays of as-long-as-designed poly-Si NWs. This process sequence is schematically shown in figure 2 and SEM images of pre- and post-filled nano-recesses are shown in figure 3.

The NW section is roughly square, with a typical dimension of 70–100 nm. Linear densities of a few thousands of NWs per mm may be achieved without stressing much the finesse of the lithography method (figure 3). N and p doped regions are locally defined after the polysilicon deposition so that the typical two legs of the thermogenerator are easily obtained.

The p-n thermopile is fabricated by alternating thermoelements composed by stacked nanowires with opposite doping type, side by side, and connecting them in series with Al interconnections, both in the hot and cold junctions. The n and p regions are obtained following thin film lithography and doping techniques common for silicon technologies: once the polysilicon is deposited, n-doping is achieved with a POCl<sub>3</sub>

**Figure 4.** (a) Lateral micro-TEG with thermoelements built with top-down defined poly-Si NWs. (b) Zoom up of the TEG lower right corner where the adjacent n and p regions are shown.

thermal process in certain areas of NWs while protecting the adjacent ones with a SiO<sub>2</sub> layer (as in the fourth diagram of figure 2(b)); the process is repeated for the p areas using a spin-on-dielectric method for Boron doping. By alternating such p and n-type multilayered nanowire arrays, a thermocouple chain is manufactured on the final micro-TEG device, around a central area of roughly  $8 \times 8 \text{ mm}^2$  (figure 4(a)). In this area, a thermal radiator can be mounted in order to enhance the thermal exchange with the surrounding environment and consequently improve the performance of thermoelectric conversion. The micro-TEG is formed by 264 n regions and 264 p regions connected in series. Every one of those regions features 78 nanowire strips, containing six nanowires each (as in figure 3(b)). The length of the nanowires is 950  $\mu$ m (a rather extreme technological case). Using smaller devices as test structures, an electrical resistivity of 2 and  $4 \,\mathrm{m}\Omega$  cm, and a Seebeck coefficient of 160 and  $140 \,\mu\text{V K}^{-1}$  have been determined for n and p-type nanowires, respectively. A Seebeck voltage of 500 mV has been obtained in preliminary measurements when letting rest one of the TEG structures of figure 4(a) onto a hotplate at 50 °C without any thermal radiator. This evidence points to the fact that such large number of Si NWs has been functionally integrated.

### Bottom-up integration of Si NWs arrays

The second approach shares with the previous one the technology used to produce the areas enabling a thermal contrast in the device (microplatforms), but makes use of bottom-up techniques to obtain the massive parallel integration of nano-objects. Since no fine lithography approach is needed at all for defining the nanowires themselves or their nanotemplates, higher Si NWs densities can be obtained at a minimum technological cost.

In this bottom-up approach, gold nanoparticles have to be selectively deposited onto the active area of the device structure: the vertical walls of the suspended platform and rim. These gold nanoparticles act as catalyst for the growth of the Si NWs by means of the chemical-vapor-deposition vapor-liquid-solid (CVD-VLS) method. The gold nanoparticles favor the decomposition of the molecules used as silicon precursors to elemental silicon. The silicon atoms are then incorporated in the gold seeds until the saturation is reached. At this point, the silicon precipitates and the epitaxial growth of the Si NWs take place till they reach the opposing wall, connecting rim and platform.

Although, neither the galvanic displacement method used for the gold seeds nor the CVD-VLS technique for NW growing are new [10–13], only recently they have been used for thermoelectric purposes [14]. Precisely, a thorough revision of the deposition conditions for both processes has been carried out in order to optimize the final Si NW array characteristics (Si NW alignment, diameter, and areal density) [15].

As mentioned above, the first step of the bottom-up approach consists on the selective gold deposition onto active areas by means of the microemulsion galvanic displacement. In this procedure, the substrate/device structure is immersed in a microemulsion prepared by mixing an aqueous solution (consisting of deionized water, NaAuCl<sub>4</sub> and HF) and an organic phase (consisting of n-heptane and AOT-surfactant). A redox reaction causes the gold precipitation onto the bare silicon surfaces. This reaction is inhibited onto those surfaces appropriately covered with silicon oxide, thus allowing the selective catalyst deposition on the areas of interest.

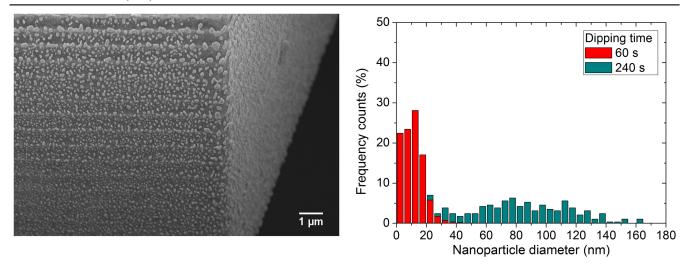

After the substrate annealing, a gold seed array is obtained (figure 5), whose mean diameter and surface density will later determine the properties of the resulting Si NW array. This way, the modification of the galvanic displacement conditions allows the control of both array parameters. The effect of varying the aqueous/organic phase proportion and the substrate dipping time were investigated. The results have showed that is possible to control the gold nanoparticles diameter in a wide range between 10 and 100 nm, and the areal density in a range between 1 and 100 nanoparticles  $\mu$ m<sup>-2</sup> [15].

Specifically, the microemulsion used for galvanic displacement seeding in the present work was obtained by mixing by sonication two phases prepared separately: (i) 1 ml of aqueous phase consisting of 0.2 M HF and 0.01 M NaAuCl<sub>4</sub> diluted in deionized water; (ii) 8 ml of organic phase consisting of 0.33 M sodium bis(2-ethylhexyl) sulfosuccinate (AOT, a surfactant) diluted in n-heptane. The dipping time was 30 s in all

**Figure 5.** Gold nanoparticles successfully deposited in the active part of the device structure: 15  $\mu$ m deep silicon trenches (left). Different gold seed size distribution obtained in a device structure by adjusting the galvanic displacement conditions (right).

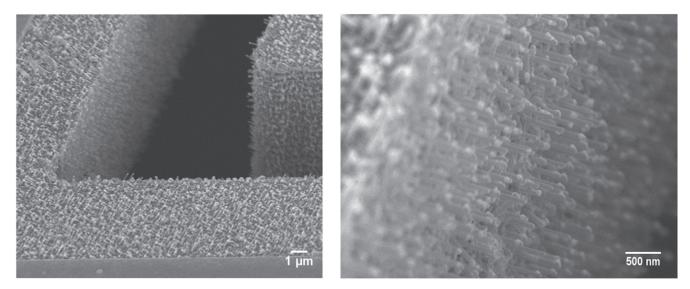

**Figure 6.** Vertical distribution of proto-Si NWs (less than 1  $\mu$ m of length) obtained in trenches after a very short CVD-VLS growth (left). Zoom up at the trench mid-section (right).

cases. Magnetic stirring was used in order to improve microemulsion penetration into the microtrenches.

Secondly, the Si NW growth conditions should be finetuned to achieve the optimum thermoelectric array. The proposed CVD process uses silane (SiH<sub>4</sub>) as NW growth precursor, which allows lower deposition temperatures more compatible with MEMS technology, instead of the commonly used silicon tetrachloride. Precisely, CVD parameters like the deposition temperature or the silane partial pressure are decisive for obtaining an array of well aligned and parallel Si NWs. Additionally, these parameters also influence on the mean diameter of the resulting Si NWs, and consequently, they should be tuned for a given gold nanoparticles size. Specifically, for a (111) silicon surface, it has been demonstrated that a deposition temperature of 650 °C and a pressure of 2.5 Torr favors obtaining Si NWs with a diameter distribution around 50–70 nm [15]. Thus, it is possible to reach a trade-off between the growth of mechanically stable Si NWs and the desired effect of phonon scattering (expected for diameters lower than 100 nm) [1]. The first stages of the NW array growth inside the device trench can be observed in figure 6, where its high density and homogeneity can be appreciated.

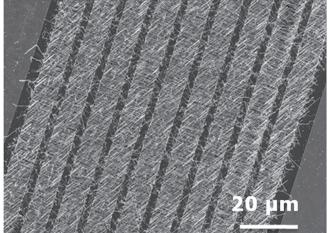

Figure 7 shows the final result after the Si NW array bridges both trench walls. The quasi-epitaxial nanowire-bulk connection obtained by means of the bottom-up approach provides a mechanically robust junction with a very low thermal and electrical contact resistance.

Since the growth of the NWs by CVD-VLS requires a  $\langle 111 \rangle$  surface and temperatures above 650 °C, the only precautions to be taken at device level are the choice of the appropriate starting silicon orientation ( $\langle 110 \rangle$ ), the topographical alignment of the perimeter of the platform with the position of vertically occurring  $\langle 111 \rangle$  planes, and the use of metals that can withstand the temperature of the CVD process (e.g. W). For technological simplicity the starting substrates

**Figure 7.** Top view of the Si NW array obtained by means of bottom-up approach, connecting rim and suspended platform. Different magnifications are presented from left to right.

chosen are SOI wafers, with a  $\langle 110 \rangle$  silicon *device* layer of several microns on top of a 500  $\mu m \langle 100 \rangle$  standard *handle* wafer with a one micron silicon oxide layer in between. The *handle* wafer is the one locally removed under the device layer for defining the suspended platforms. The thickness of the silicon *device* layer together with the perimeter of the platform and the areal density of gold seeds determine the number of Si NWs that will be obtained in the device. The architecture proposed for the thermoelectric generator is unileg, which means that only one type (p-type) of semiconductor is used, while the second thermoelectric leg is made of metal (figure 8). A p-type Si NW array is achieved by simply introducing diborane (B<sub>2</sub>H<sub>6</sub>) during the CVD growth process, while the doping level is controlled by means of the diborane partial pressure [16].

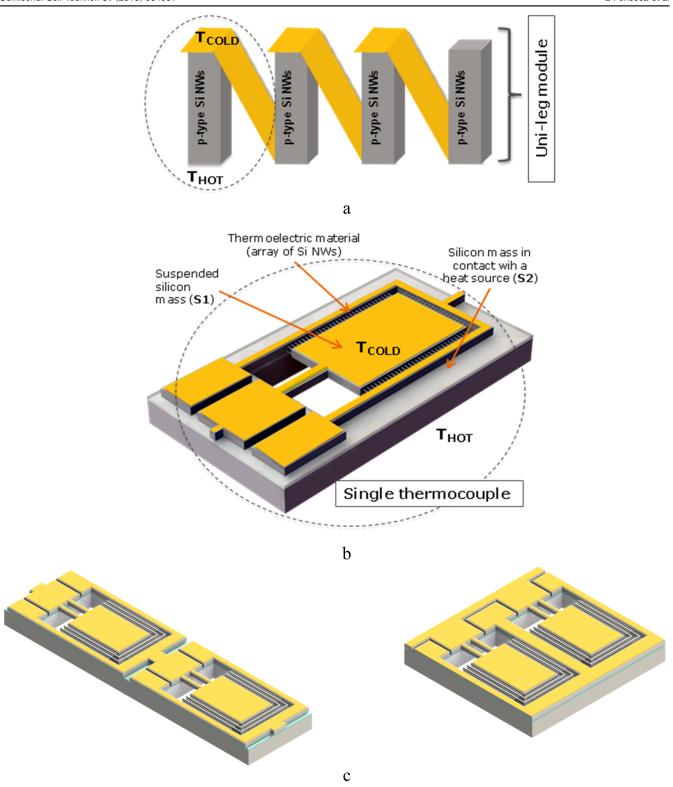

The resulting TEG performance is 'halved' but the technology is kept simple. This uni-leg approach is common in planar thin film thermopiles used as infrared sensors. Figure 8(b) shows how the uni-leg configuration is materialized in our planar approach: the suspended platform and surrounding rim configure one single uni-leg thermocouple (corresponding to the dotted circle of figure 8(a)) of the final thermopile, where the Si NWs distributed across the perimeter of the platform and connecting it to the rim are the p-leg and the metal track going from the platform to rim through the silicon supporting bridge is the metal leg. Microplatforms such the ones described have been fabricated and Si NWs have been successfully integrated in large numbers as can be seen in figure 9.

Although both top-down and bottom-up approaches use a similar planar architecture, it must be stressed that the suspended platform in the case of the top-down approach configures a *whole thermopile* (with several p—n thermocouples) while for the bottom-up approach the suspended platform configures a *single uni-leg thermocouple* and several of them need to be fabricated in parallel and connected to produce a uni-leg thermopile. Consequently, the suspended platform in the top-down approach is large (ca 1 cm<sup>2</sup>) but small for the bottom-up approach (ca 1 mm<sup>2</sup>).

With appropriate Si NWs doping, resistances as low as  $60\,\Omega$  have been measured for the NWs ensemble in devices like the ones of figure 9; this resistance corresponds to a great extent to the metal collectors, pointing to a good electric contact of the NWs with the silicon areas they are grown from. Preliminary characterization shows that one of those bottom-up thermocouples produces about 90 nW when placed onto a 250 °C hot plate. The lack of a heat exchanger limits the effective  $\Delta T$  perceived by the Si NWs and the corresponding harvested power. If that same temperature is forced locally in the suspended platform by means of the built-in heater shown in figure 9(a), the power obtained reaches  $10\,\mu\mathrm{W}$ , which clearly points to the need of a heat exchanger that maximizes the temperature across the nanowires while in operation.

### Optimal density of Si NWs arrays

It becomes clear that both approaches offer an important control capability of the NW array properties. This trait is of special interest to maximize the device performance, since it is well known the need of finding an optimal trade-off between the electrical resistance and thermal resistance of the TEG [17].

For a thermoelectric device, it can be shown that the maximum power in load matching conditions  $P_{\rm out}$  is described by the following formula:

$$P_{\text{out}} = \frac{(N_{\text{TE}}S\Delta T)^2}{4N_{\text{TE}}R_{\text{TE}}} \tag{1}$$

in which S is the Seebeck coefficient of the individual nanostructured thermoelement,  $R_{\rm TE}$  its electrical resistance,  $\Delta T$  the temperature difference which builds up across the thermoelements when the device is operating, and  $N_{\rm TE}$  the number of thermoelements connected in series in the generator. Equation (1) is derived from the electrical power transferred to an output load in matching conditions from a linear network with output resistance  $R_{\rm out}$  and equivalent Thévenin voltage source  $V_{\rm eq}$ , equal to  $P_{\rm out} = V_{\rm eq}^2/(4R_{\rm eq})$ . For

**Figure 8.** (a) Sketch of a uni-leg approach: only one polarity semiconductor is used, the second leg is made of metal. (b) Schematics of the unitary thermocouple formed by the metal track and the bridging Si NWs array in a suspended platform planar configuration; it corresponds to the physical implementation of the dotted circle in figure 8(a). (c) In-chip arrangements of several termocouples with appropriate series or parallel connections are needed to define the final micro-TEG with appropriate V and I characteristics.

the particular case of a thermoelectric generator, the identities  $V_{\rm eq}=N_{\rm TE}S\Delta T$  and  $R_{\rm eq}=N_{\rm TE}R_{\rm TE}$  hold.

Specifically, the Si NW areal density becomes the key parameter in this optimization process once the generator

structure properties (parasitic thermal and electrical resistance) and the thermoelectric material properties (thermal conductivity,  $\kappa_{\rm SiNW}$ , electrical resistivity,  $\rho_{\rm SiNW}$ , and Seebeck coefficient,  $S_{\rm SiNW}$ ) are set.

**Figure 9.** Lateral high density crystalline Si NWs arrays bridging the suspended microplatform and the surrounding device rim. A multitrench strategy using intermediate narrow Si spacers has been adopted here to obtain 'effective' longer NWs after a single  $10 \mu m$  NW CVD-VLS process (left). Zoom up of a section of the bridging area with nine consecutive filled trenches (right) [14].

**Table 1.** Si NW parameters used for the bottom-up micro-TEG performance modeling. Electrical properties correspond to a boron doping level of 10<sup>18</sup> cm<sup>-3</sup>. Thermal conductivity corresponds to a Si NW mean diameter in the order of 50 nm.

| Length $(\mu m)$ | $ ho_{ m SiNW}$ (m $\Omega$ cm) | $S_{ m SiNW} \ (\mu  m V  m K^{-1})$ | $({ m W}  { m m}^{-1}  { m K}^{-1})$ |

|------------------|---------------------------------|--------------------------------------|--------------------------------------|

| 10               | 48                              | 970                                  | 10                                   |

# Bottom-up approach

In order to theoretically determine the influence of NW array density (among other parameters) on device performance, an analytical device model has been developed that includes the main features of the proposed uni-leg bottom-up micro-TEG design and the typical thermoelectric Si NW properties (summarized in table 1) [1, 16, 18].

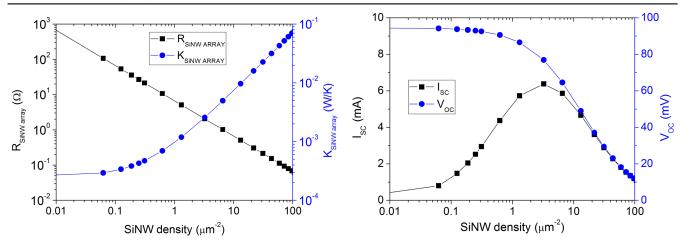

Being the NWs assembled in a parallel configuration, the progressive increase of the Si NW array density leads to a reduction of its effective resistance ( $R_{\rm SiNW}$  array), thus improving the device internal resistance and its maximum short-circuit electrical current ( $I_{\rm SC}$ ). However, this effect is limited by the generator parasitic electrical resistance, and counterbalanced by the greater thermal conductance of the Si NW array ( $K_{\rm SiNW}$  array) that causes a thermal gradient drop. As a result, the initial  $I_{\rm SC}$  improvement curves down at very high array densities, associated to a worsening of the maximum open-circuit voltage ( $V_{\rm OC}$ ). Both effects are appreciated in figure 10, in which a temperature gradient of 100 K is considered.

Thus, the model confirms the existence of a proper NW  $\mu m^{-2}$  value that enhances the device performance. Specifically, it has been found that for typical Si NW thermal conductivities, the optimum array density is in the range of 0.1–10 NW  $\mu m^{-2}$ . Moreover, results in figure 11 show that for low enough  $\kappa_{\rm SiNW}$ , maximum power values of the order of 100–200  $\mu$ W could be achieved with a temperature gradient of 100 K. Similarly, changes in the Si NW doping level

require an array density adjustment in order to maximize the device performance. Again, optimum areal densities are found in the range of 0.1–10 NW  $\mu m^{-2}$ , confirming the feasibility of a fully optimized micro-TEG. The power values have been calculated using equation (1) with  $N_{\rm TE}=1$  (single thermocouple with thermal and electrical parallel arrangement of NWs).

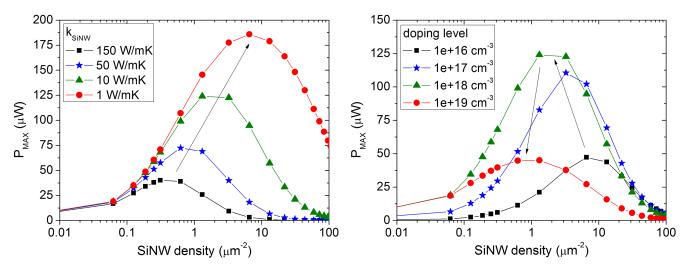

#### Top-down approach

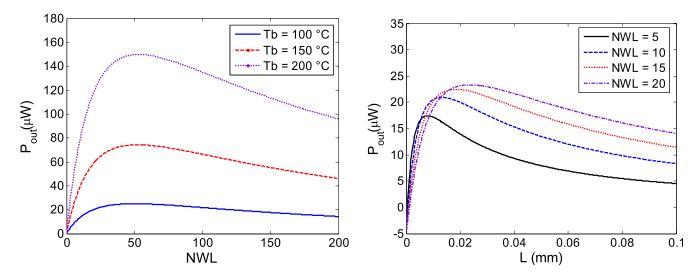

For the top-down approach, similar considerations can be formulated about the nanowire density for a fixed length of the thermoelements that are composed by nanowires connected thermally in parallel and electrically in series. It can be shown that the thermal behavior of the top-down TEG structure can be approximately described by an analytical model [19]. Figure 12 (left) reports the power generated by the top-down TEG versus the number of nanowire levels (NWL) used in the stacked array, calculated using such analytical model with physical parameters measured on heavily doped polycrystalline silicon nanowires in previous works [5, 20]. As can be seen, also in this case an optimum NWL (and consequently an optimum nanowire density) exists. However, such optimized value is different when the length of the thermoelement is varied, as shown in figure 12 (right).

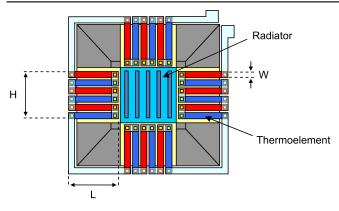

As far as the series connection of the thermocouples is concerned, a reference geometry like the one shown in figure 13 can be considered for the top-down device. Assuming than all the available space in the device around the radiator area is utilized to accommodate the largest possible number of thermoelements, the temperature difference  $\Delta T$  will be, to a first-level approximation, independent of the type of arrangement chosen for the thermoelements because this will weakly affect the thermal resistance of the generator. Moreover, by indicating with W the width of the thermoelement (figure 13), it can be noted that, in order to increase the number of thermocouples connected in series, their width will

**Figure 10.** Evolution of the modeled Si NW array electrical and thermal properties as the array density is increased (left). Evolution of the modeled short-circuit current and open-circuit voltage as the array density is increased (right). Table 1 parameters are used.

**Figure 11.** Maximum power dependence on the array density for different Si NW thermal conductivity values (left) and for different Si NW doping levels (right). A doping level of  $10^{18}$  cm<sup>-3</sup> and a  $\kappa_{\text{SiNW}}$  of 10 W m<sup>-1</sup> K<sup>-1</sup> are respectively considered.

Figure 12. Calculated output power dependence on NWL ( $L=50~\mu m$ ) for different hot body temperatures (left) and on L (Tb =  $100~^{\circ}$ C) for different NWLs (right). The lateral distance between vertical NW stacks is set to 200~nm.

Figure 13. Top-view of top-down thermoelectric generator.

have to be decreased since for space limitations the maximum number of thermoelements in the device will be equal to 4 H/W. As a consequence, both  $N_{\rm TE}$  and  $R_{\rm TE}$  will be proportional to 1/W, and, as per equation (1),  $P_{\rm out}$  will turn out to be independent of W or, equivalently, of  $N_{\rm TE}$ . Therefore, to a first approximation, the same maximum converted power is expected for equal devices which only differ in the number of series-connected thermocouples. This will not hold for the output voltage that, on the contrary, will be proportional to  $N_{\rm TE}$ .

#### **Conclusions**

Two approaches for obtaining stacked Si-based NWs arrays of medium-high density have been presented. Both approaches make use of silicon technologies and compatible materials and processes. Specifically, such technologies are used to produce 3D architectures with suspended silicon membranes that offer areas of thermal contrast where to integrate nanoobjects of thermoelectric relevance. Single crystalline and polycrystalline silicon nanowires of arbitrary length and with effective diameters below 100 nm have been successfully obtained so that phonon scattering phenomena will lead to high enough ZT values. Tens or hundreds of thousands of NWs readily connected can be obtained. In the first case considered, the top-down approach typical of silicon technology has been extended to define polysilicon stacked nanowires arrays from thin multilayers exploiting a smart sequential combination of thin film deposition and etch steps using only standard silicon materials. In the second case, a bottom-up approach has been used to obtain dense bundles of laterally oriented crystalline silicon nanowires across vertical silicon scaffolds, achieving parallel integration of large number of nanowires at a minimum technological cost. NWs densities attainable with both methods have been shown to be in line with the optimum range needed for maximizing TEG power output for typical NWs doping levels and expected thermal conductivities. Preliminary electrical parameters of the nanowires ensembles have been measured on-chip demonstrating that both approaches have led to successful integration. Next steps will involve the performance characterization of both types of Si-based NWs arrangements into TEG devices. In both cases, the ultimate goal is the monolithic integration of all-silicon thermoelectric micronanogenerators that can be fabricated cost-effectively in large volumes with minimal material and technological complexity (avoiding for instance time-consuming nanolithography processes). Such micro-nanogenerators could be used as power sources for the deployment of autonomous microsensors where waste heat sources are present.

## **Acknowledgments**

This work was supported by FP7-NMP-2013-SMALL-7, SiNERGY (Silicon Friendly Materials and Device Solutions for Microenergy Applications), Contract 604169.

#### References

- [1] Hochbaum A I, Chen R, Diaz Delgado R, Liang W, Garnett E C, Najarian M, Majumdar A and Yang P 2008 Enhanced thermoelectric performance of rough silicon nanowires *Nature* 451 163–7

- [2] Boukai A I, Bunimovich Y, Tahir-Khel J, Yu J K, Goddard W A III and Heath J R 2008 Silicon nanowires as efficient thermoelectric materials *Nature* 451 168–71

- [3] Liu W and Asheghi M 2006 Thermal conductivity measurements of ultra-thin single crystal silicon layers J. Heat Transfer. 128 75–83

- [4] Li Y, Buddharaju K, Singh N and Lee S J 2012 Top-down silicon nanowire-based thermoelectric generator: design and characterization J. Electron. Mater. 41 989–92

- [5] Suriano F, Ferri M, Moscatelli F, Mancarella F, Belsito L, Solmi S, Roncaglia A, Frabboni S, Gazzadi G C and Narducci D 2015 Influence of grain size on the thermoelectric properties of polycrystalline silicon nanowires J. Electron. Mater. 44 371–6

- [6] Yang F and Dames C 2013 Mean free path spectra as a tool to understand thermal conductivity in bulk and nanostructures *Phys. Rev.* B 87 035437

- [7] Narducci D, Cerofolini G F, Ferri M, Suriano F, Mancarella F, Belsito L, Solmi S and Roncaglia A 2013 Phonon scattering enhancement in silicon nanolayers J. Mater. Sci. 48 2779–84

- [8] Suriano F, Ferri M, Solmi S, Belsito L, Roncaglia A, Romano E, Narducci D and Cerofolini G 2012 Thermoelectric properties of p and n-type nanocrystalline silicon nanowires with high doping levels MRS Proc. 1408

- [9] Ferri M, Suriano F, Roncaglia A, Solmi S, Cerofolini G F, Romano E and Narducci D 2012 Ultradense silicon nanowire arrays produced via top-down planar technology *Microelectron. Eng.* 88 877–81

- [10] Magagnin L, Bertani V, Cavallotti P L, Maboudia R and Carraro C 2002 Selective deposition of gold nanoclusters on silicon by a galvanic displacement process *Microelectron*. *Eng.* 64 479–85

- [11] Gao D, He R, Carraro C, Howe R T, Yang P and Maboudian R 2005 Selective growth of Si nanowire arrays via galvanic displacement processes in water-in-oil microemulsions J. Am. Chem. Soc. 127 4574–5

- [12] Doerk G S, Dhong C, Politi C, Laboriante I, Carraro C and Maboudian R 2011 Micellar block copolymer template galvanic displacement for epitaxial nanowire device integration J. Mater. Chem. 21 8807

- [13] Paulo A S, Arellano N, Plaza J A, He R, Carraro C, Maboudian R, Howe R T, Bokor J and Yang P 2007 Suspended mechanical structures based on elastic silicon nanowire arrays *Nano Lett.* 7 1100–4

- [14] Dávila D, Tarancón A, Calaza C, Salleras M, Fernández-Regúlez M, Paulo A S and Fonseca L 2012 Monolithically integrated thermoelectric energy harvester based on silicon nanowire arrays for powering micro/ nanodevices *Nano Energy* 1 812–9

- [15] Gadea G, Morata A, Santos J D, Dávila D, Calaza C, Salleras M, Fonseca L and Tarancón A Towards a full integration of vertically aligned silicon nanowires in MEMS using silane as a precursor 2015 Nanotechnology 26 195302

- [16] Wallenting J and Borgström M T 2011 Doping of semiconductor nanowires J. Mater. Res. 26 2142–56

- [17] Apertet A, Ouerdane H, Glavatskaya O, Goupil C and Lecoeur P 2012 Optimal working conditions for thermoelectric generators with realistic thermal coupling *Europhys. Lett.* 97 28001

- [18] Geballe T and Hull G 1955 Seebeck effect in silicon *Phys. Rev.* **98** 940–7

- [19] Roncaglia A and Ferri M 2011 Thermoelectric materials in MEMS and NEMS: a review Sci. Adv. Mater. 3 401–19

- [20] Mancarella F, Roncaglia A and Cardinali G C 2006 A measurement technique for thermoelectric power of CMOS layers at the wafer-level *Sensor Actuators* A 132 289–95