## UNIVERSITÀ DEGLI STUDI DI MILANO-BICOCCA Dipartimento di Fisica "G. Occhialini"

Scuola di Dottorato in Scienze Ciclo XXVIII

## Design and Development of an Integrated Readout System for the Triple-GEM Detector

#### Alessandro Pezzotta

Tutor: Prof. Andrea Baschirotto

Tesi di Dottorato in Fisica e Astronomia Settore Scientifico-Disciplinare: FIS/01

Anno Accademico 2014/2015

## Contents

| I  | Pre        | eface                                                                                                                | 1                |

|----|------------|----------------------------------------------------------------------------------------------------------------------|------------------|

| 1  | 1.1<br>1.2 | Background and Motivations The GEM Detector 1.2.1 Basic principles of functioning 1.2.2 Recent Developments: BANDGEM | 3<br>4<br>4<br>7 |

|    | 1.3        | The State-of-the-Art on Readout Electronics                                                                          | 8                |

| II | G          | EMMA Prototype                                                                                                       | 9                |

| 2  | Fron       | nt-End                                                                                                               | 11               |

|    | 2.1        | GEM Detector signal modeling                                                                                         | 11               |

|    | 2.2        | GEMMA Signals                                                                                                        | 11               |

|    | 2.3        | Detection Chain                                                                                                      | 12               |

|    | 2.4        |                                                                                                                      | 14               |

|    |            | 1 1                                                                                                                  | 14               |

|    | 2.5        | 8                                                                                                                    | 14               |

|    |            | 2.5.1 Calibration circuit general description                                                                        | 14               |

|    |            | O                                                                                                                    | 19               |

|    |            | 2.5.3 Calibration Digital Section                                                                                    | 30               |

| 3  | Lay        | out                                                                                                                  | 37               |

|    | 3.1        | Design rules and guidelines                                                                                          | 37               |

|    | 3.2        |                                                                                                                      | 38               |

|    |            | 1                                                                                                                    | 38               |

|    |            |                                                                                                                      | 39               |

|    |            | 8                                                                                                                    | 40               |

|    | 3.3        |                                                                                                                      | 41               |

|    | 3.4        | ,                                                                                                                    | 42               |

|    |            | 3.4.1 Pins structure and position                                                                                    | 43               |

| 4  | Perf       | ormance                                                                                                              | 47               |

|    | 4.1        |                                                                                                                      | 47               |

|    |            | ,                                                                                                                    | 49               |

|    |            | 4.1.2 Noise simulation                                                                                               | 50               |

ii CONTENTS

|    | 4.2         | Measu   | rements                               | 52       |

|----|-------------|---------|---------------------------------------|----------|

|    |             | 4.2.1   | Main Signals                          | 52       |

|    |             | 4.2.2   | Linearity                             | 53       |

|    |             | 4.2.3   | · · · · · · · · · · · · · · · · · · · | 54       |

|    |             |         |                                       |          |

| II | I C         | EMIN    | II Prototype                          | 55       |

| 5  | Fron        | nt-End  |                                       | 57       |

| 5  | 5.1         |         |                                       | 57       |

|    | 5.2         |         |                                       | 57<br>57 |

|    | O. <u>_</u> | 5.2.1   | 0                                     | 57       |

|    |             | 5.2.2   | O I                                   | 59       |

|    |             | 5.2.3   |                                       | 61       |

|    |             | 5.2.4   |                                       | 62       |

|    |             | 5.2.5   | 00                                    | 62       |

|    |             | 5.2.6   |                                       | 63       |

|    |             |         |                                       |          |

| 6  | Lay         |         |                                       | 65       |

|    | 6.1         |         | ,                                     | 65       |

|    | 6.2         |         | 3                                     | 65       |

|    |             | 6.2.1   | O I                                   | 65       |

|    |             | 6.2.2   |                                       | 66       |

|    |             | 6.2.3   |                                       | 66       |

|    |             | 6.2.4   | Whole channel and core                | 67       |

| 7  | Perf        | ormanc  | ee                                    | 69       |

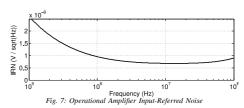

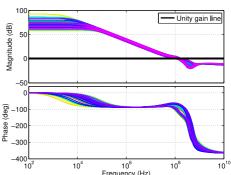

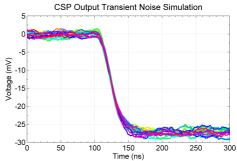

|    | 7.1         | Transie | ent Noise Monte Carlo CSP Simulation  | 69       |

|    | 7.2         |         |                                       | 70       |

|    |             | 7.2.1   | Test Equipment                        | 70       |

|    |             | 7.2.2   |                                       | 72       |

|    |             | 7.2.3   | Č                                     | 73       |

|    | 7.3         | Noise   |                                       | 74       |

|    |             |         |                                       |          |

| I  | / <b>P</b>  | apers   | "                                     | 75       |

| 8  | GEN         | MMA R   | elated Papers                         | 77       |

|    | 8.1         |         | •                                     | 78       |

|    | 8.2         | IEEE IO | CICDT 2013                            | 82       |

|    | 8.3         |         |                                       | 86       |

| 0  | CEN         | AINH P  | olated Damage                         | 02       |

| 9  |             |         | T                                     | 93       |

|    | 9.1         |         |                                       | 94<br>98 |

|    | 7.4         | TEEE    | (ENDUND 2010                          | 70       |

| C  | ONTENTS                                               | iii            |

|----|-------------------------------------------------------|----------------|

| V  | Conclusions                                           | 103            |

| 10 | Conclusions 10.1 Comparison with the state of the art | <b>105</b> 105 |

| Bi | bliography                                            | 107            |

#4

## **List of Figures**

| 1.2       Electric field lines in a GEM (from CERN GDD Group)       6         1.3       Structure and gain of a GEM (courtesy of F. Murtas)       6         1.4       GEM typical configuration (courtesy of F. Murtas)       7         1.5       The BANDGEM configuration (courtesy of G. Croci)       8         2.1       GEM detector front-end, block scheme       11         2.2       GEM detector modeling       12         2.3       Event detection impulse (EDS) diagram       12         2.4       CTS diagram       13         2.5       GEMMA Front-end complete scheme       13         2.6       Operational Amplifier schematic       15         2.7       The calibration ramp in nominal conditions       16         2.8       Algorithm of the tuning process       17         2.9       The capacitor values related to the digital words       18         2.10       Matlab simulation results       18         2.11       Low-level diagram of the tuning machine       19         2.12       Alternative low-level diagram of the tuning machine       19         2.13       Operational Amplifier       20         2.14       Op-Amp schematic       20 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.4 GEM typical configuration (courtesy of F. Murtas) 7 1.5 The BANDGEM configuration (courtesy of G. Croci) 8 2.1 GEM detector front-end, block scheme 11 2.2 GEM detector modeling 12 2.3 Event detection impulse (EDS) diagram 12 2.4 CTS diagram 13 2.5 GEMMA Front-end complete scheme 13 2.6 Operational Amplifier schematic 15 2.7 The calibration ramp in nominal conditions 16 2.8 Algorithm of the tuning process 17 2.9 The capacitor values related to the digital words 18 2.10 Matlab simulation results 18 2.11 Low-level diagram of the tuning machine 19 2.12 Alternative low-level diagram of the tuning machine 19 2.13 Operational Amplifier 20 2.14 Op-Amp schematic 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.4 GEM typical configuration (courtesy of F. Murtas) 7 1.5 The BANDGEM configuration (courtesy of G. Croci) 8 2.1 GEM detector front-end, block scheme 11 2.2 GEM detector modeling 12 2.3 Event detection impulse (EDS) diagram 12 2.4 CTS diagram 13 2.5 GEMMA Front-end complete scheme 13 2.6 Operational Amplifier schematic 15 2.7 The calibration ramp in nominal conditions 16 2.8 Algorithm of the tuning process 17 2.9 The capacitor values related to the digital words 18 2.10 Matlab simulation results 18 2.11 Low-level diagram of the tuning machine 19 2.12 Alternative low-level diagram of the tuning machine 19 2.13 Operational Amplifier 20 2.14 Op-Amp schematic 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.5 The BANDGEM configuration (courtesy of G. Croci)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2       GEM detector modeling       12         2.3       Event detection impulse (EDS) diagram       12         2.4       CTS diagram       13         2.5       GEMMA Front-end complete scheme       13         2.6       Operational Amplifier schematic       15         2.7       The calibration ramp in nominal conditions       16         2.8       Algorithm of the tuning process       17         2.9       The capacitor values related to the digital words       18         2.10       Matlab simulation results       18         2.11       Low-level diagram of the tuning machine       19         2.12       Alternative low-level diagram of the tuning machine       19         2.13       Operational Amplifier       20         2.14       Op-Amp schematic       20                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.2       GEM detector modeling       12         2.3       Event detection impulse (EDS) diagram       12         2.4       CTS diagram       13         2.5       GEMMA Front-end complete scheme       13         2.6       Operational Amplifier schematic       15         2.7       The calibration ramp in nominal conditions       16         2.8       Algorithm of the tuning process       17         2.9       The capacitor values related to the digital words       18         2.10       Matlab simulation results       18         2.11       Low-level diagram of the tuning machine       19         2.12       Alternative low-level diagram of the tuning machine       19         2.13       Operational Amplifier       20         2.14       Op-Amp schematic       20                                                                                                                                                                                                                                                                                                                                                                                    |

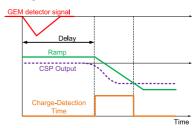

| 2.3       Event detection impulse (EDS) diagram       12         2.4       CTS diagram       13         2.5       GEMMA Front-end complete scheme       13         2.6       Operational Amplifier schematic       15         2.7       The calibration ramp in nominal conditions       16         2.8       Algorithm of the tuning process       17         2.9       The capacitor values related to the digital words       18         2.10       Matlab simulation results       18         2.11       Low-level diagram of the tuning machine       19         2.12       Alternative low-level diagram of the tuning machine       19         2.13       Operational Amplifier       20         2.14       Op-Amp schematic       20                                                                                                                                                                                                                                                                                                                                                                                                                                     |

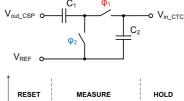

| 2.4CTS diagram132.5GEMMA Front-end complete scheme132.6Operational Amplifier schematic152.7The calibration ramp in nominal conditions162.8Algorithm of the tuning process172.9The capacitor values related to the digital words182.10Matlab simulation results182.11Low-level diagram of the tuning machine192.12Alternative low-level diagram of the tuning machine192.13Operational Amplifier202.14Op-Amp schematic20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

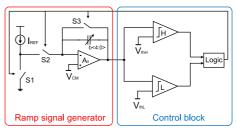

| 2.5GEMMA Front-end complete scheme132.6Operational Amplifier schematic152.7The calibration ramp in nominal conditions162.8Algorithm of the tuning process172.9The capacitor values related to the digital words182.10Matlab simulation results182.11Low-level diagram of the tuning machine192.12Alternative low-level diagram of the tuning machine192.13Operational Amplifier202.14Op-Amp schematic20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

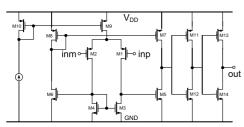

| 2.6 Operational Amplifier schematic152.7 The calibration ramp in nominal conditions162.8 Algorithm of the tuning process172.9 The capacitor values related to the digital words182.10 Matlab simulation results182.11 Low-level diagram of the tuning machine192.12 Alternative low-level diagram of the tuning machine192.13 Operational Amplifier202.14 Op-Amp schematic20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.7 The calibration ramp in nominal conditions162.8 Algorithm of the tuning process172.9 The capacitor values related to the digital words182.10 Matlab simulation results182.11 Low-level diagram of the tuning machine192.12 Alternative low-level diagram of the tuning machine192.13 Operational Amplifier202.14 Op-Amp schematic20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.8 Algorithm of the tuning process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.9 The capacitor values related to the digital words182.10 Matlab simulation results182.11 Low-level diagram of the tuning machine192.12 Alternative low-level diagram of the tuning machine192.13 Operational Amplifier202.14 Op-Amp schematic20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.10 Matlab simulation results182.11 Low-level diagram of the tuning machine192.12 Alternative low-level diagram of the tuning machine192.13 Operational Amplifier202.14 Op-Amp schematic20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.11 Low-level diagram of the tuning machine192.12 Alternative low-level diagram of the tuning machine192.13 Operational Amplifier202.14 Op-Amp schematic20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.12 Alternative low-level diagram of the tuning machine       19         2.13 Operational Amplifier       20         2.14 Op-Amp schematic       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.13 Operational Amplifier       20         2.14 Op-Amp schematic       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.14 Op-Amp schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

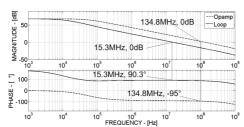

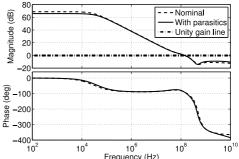

| 2.15 Op-Amp frequency response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

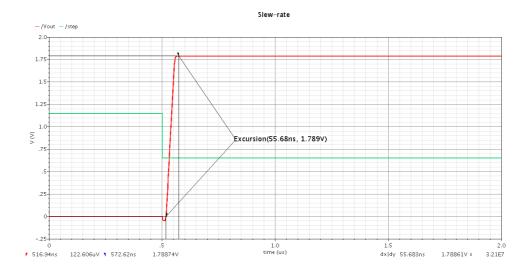

| 2.16 Op-Amp step response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.17 Op-Amp power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.18 Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.19 High threshold comparator schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.20 Low threshold comparator schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

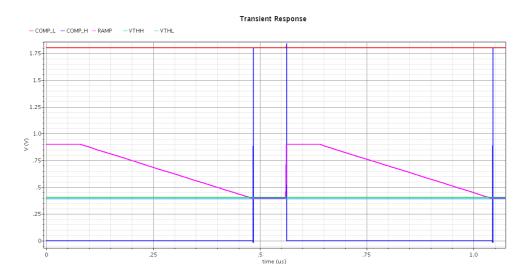

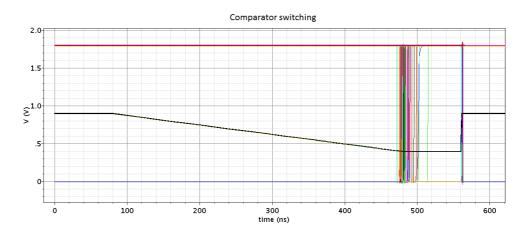

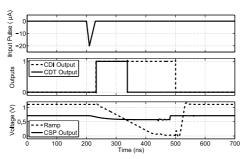

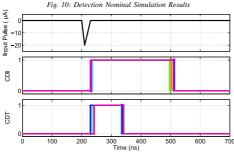

| 2.21 Comparators response in nominal conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.22 Comparators response with a Monte Carlo simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

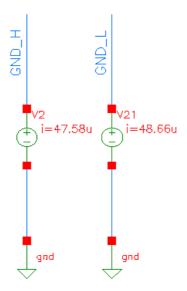

| 2.23 Comparators power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

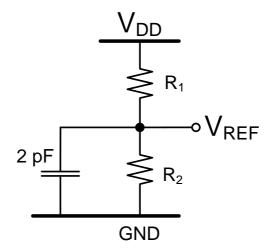

| 2.24 Voltage references architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.25 Capacitor array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.26 Schematic of the capacitor array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.27 Schematic of the "cap array switch" block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.28 Automatic digital synthesis tool structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

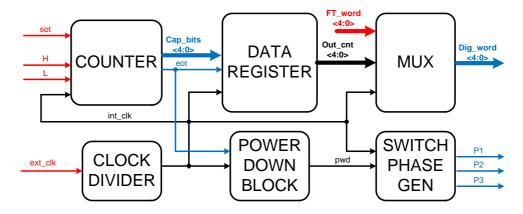

| 2.29 The Digital Part block scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

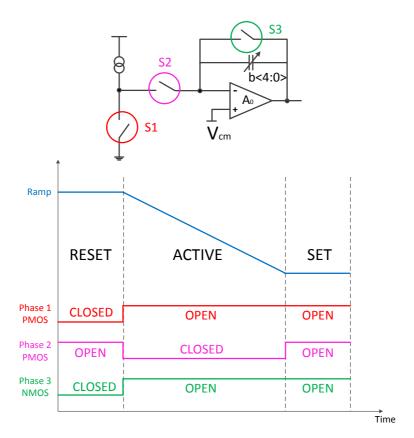

| 2.30 | Switch phases                                                        | 32 |

|------|----------------------------------------------------------------------|----|

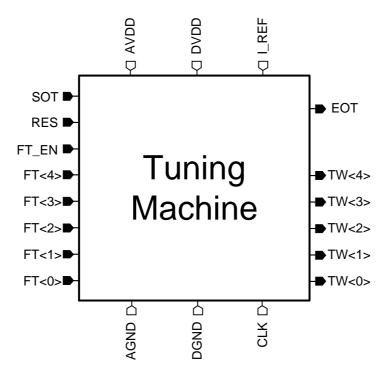

| 2.31 | High-level diagram of the tuning machine                             | 34 |

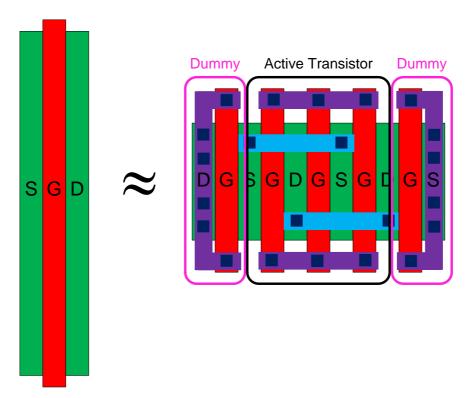

| 3.1  | Transistor layout: without and with fingers and dummies              | 38 |

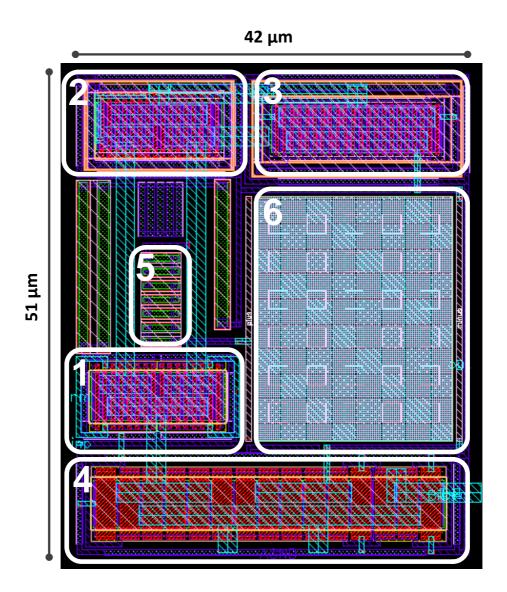

| 3.2  | Calibration circuit opamp layout                                     | 39 |

| 3.3  | Calibration circuit comparators layout: the high one is on top while |    |

|      | the low one is on the bottom                                         | 40 |

| 3.4  | Capacitors array layout                                              | 41 |

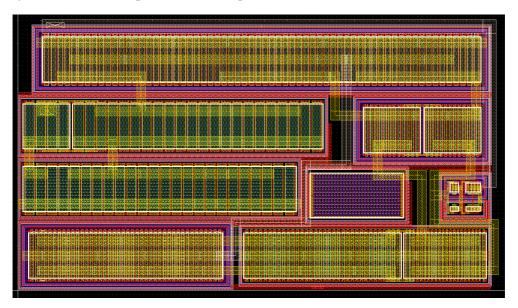

| 3.5  | Analog section of the calibration circuit layout                     | 42 |

| 3.6  | Calibration circuit digital block layout                             | 43 |

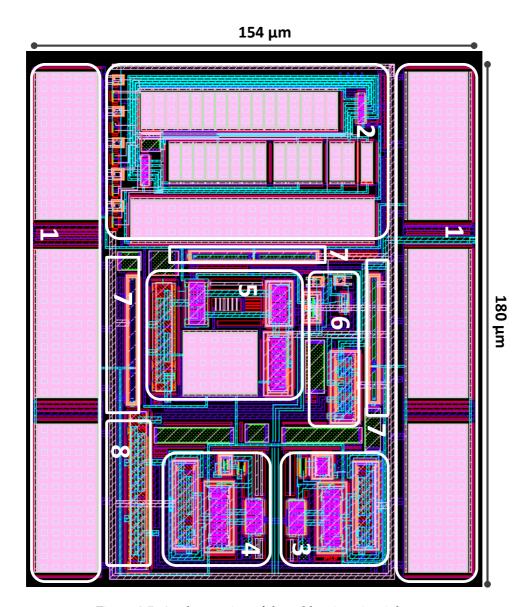

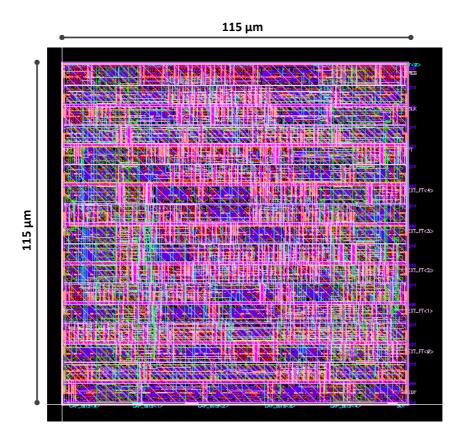

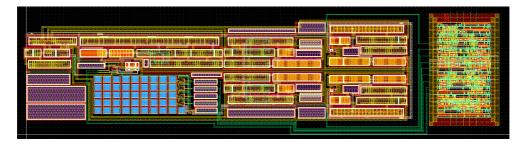

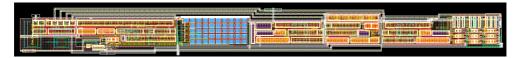

| 3.7  | ASIC complete layout                                                 | 44 |

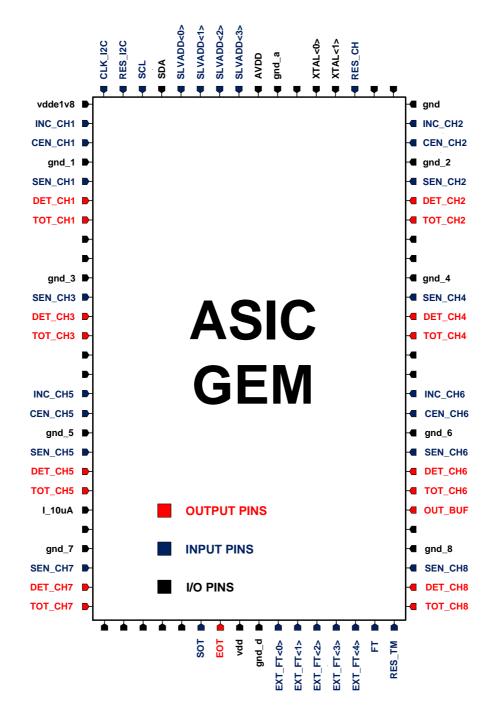

| 3.8  | ASIC pin structure                                                   | 45 |

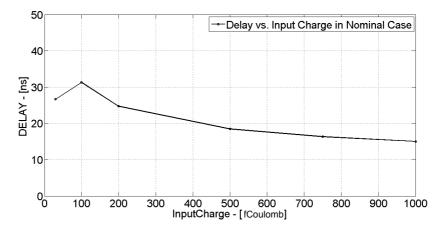

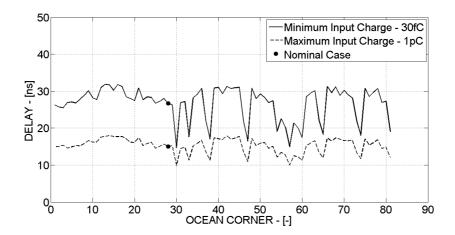

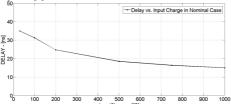

| 4.1  | EDS delay vs. input charge in nominal case (from 30 fC to 1 pC)      | 49 |

| 4.2  | EDS delay vs. simulation corner (for 30 fC and 1 pC input charge)    | 49 |

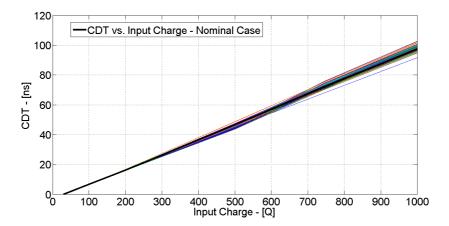

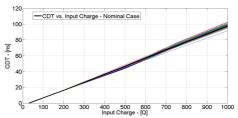

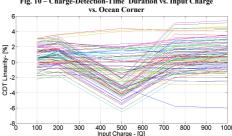

| 4.3  | CTS duration vs. input charge vs. simulation corner                  | 50 |

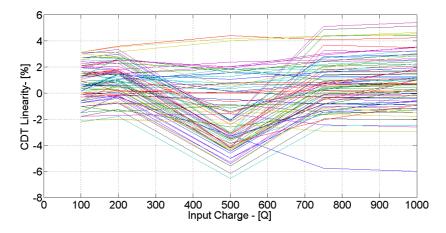

| 4.4  | CTS linearity error vs. input charge vs. simulation corner           | 50 |

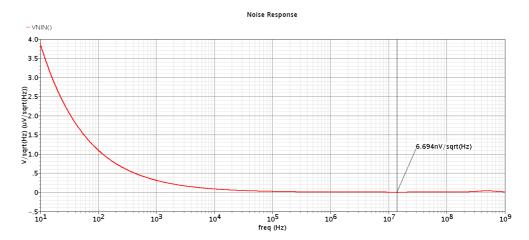

| 4.5  | Preamplifier opamp IRN                                               | 51 |

| 4.6  | GEMMA Signals for 30 fC Charge                                       | 52 |

| 4.7  | GEMMA Signals for 1 pC Charge                                        | 52 |

| 4.8  | EDS Delay vs. Input Charge                                           | 53 |

| 4.9  | CTS Duration vs. Input Charge                                        | 53 |

| 4.10 | ENC vs. Pad Capacitance                                              | 54 |

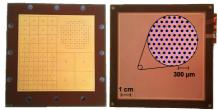

| 5.1  | GEM Output Pads                                                      | 58 |

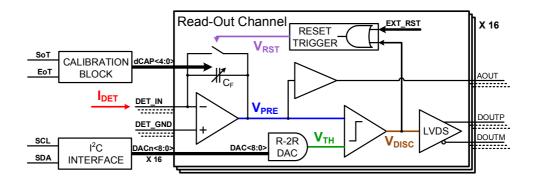

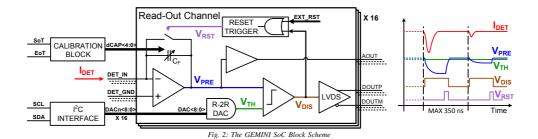

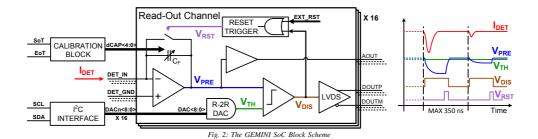

| 5.2  | The GEMINI SoC Block Scheme                                          | 59 |

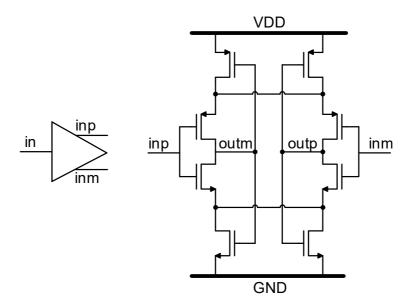

| 5.3  | GEMINI Operational Amplifier schematic                               | 60 |

| 5.4  | GEMINI Discriminator schematic                                       | 61 |

| 5.5  | GEMINI DAC schematic                                                 | 62 |

| 5.6  | GEMINI LVDS Driver schematic                                         | 63 |

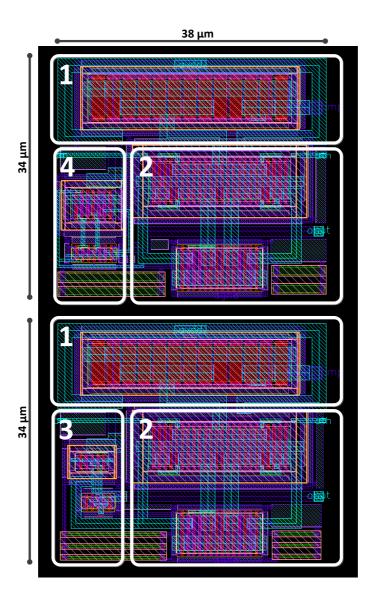

| 6.1  | Calibration circuit layout                                           | 65 |

| 6.2  | Preamplifier layout                                                  | 65 |

| 6.3  | Capacitors array layout                                              | 66 |

| 6.4  | R-2R Threshold DAC layout                                            | 66 |

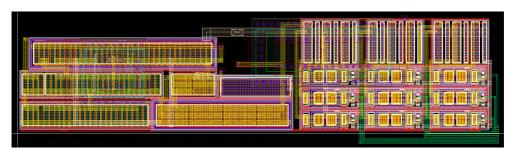

| 6.5  | Detecting channel layout                                             | 67 |

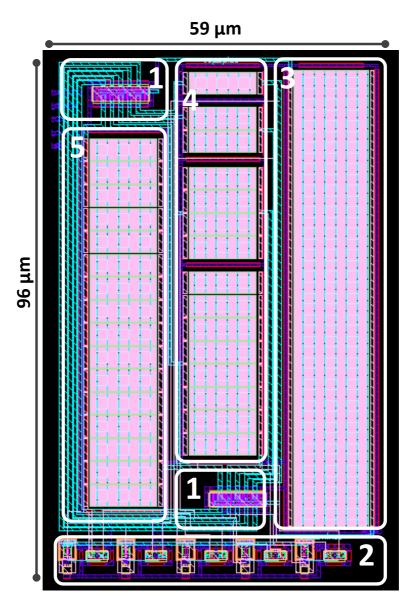

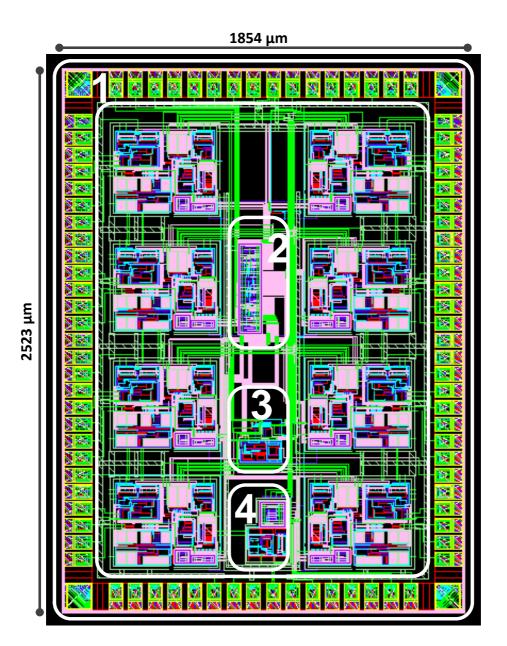

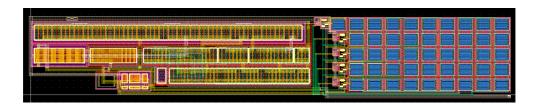

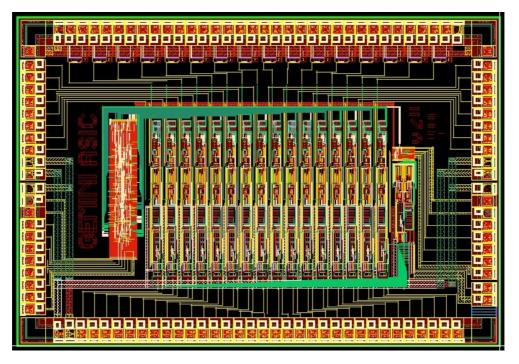

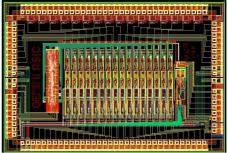

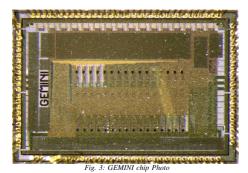

| 6.6  | GEMINI ASIC complete layout                                          | 67 |

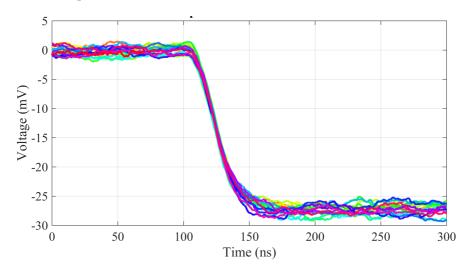

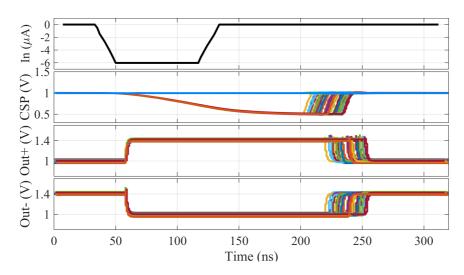

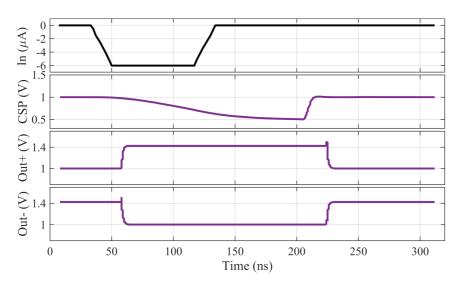

| 7.1  | Post-Layout Transient Noise CSP Simulation                           | 69 |

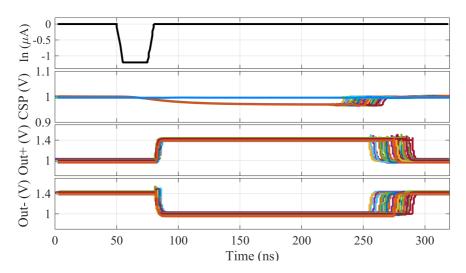

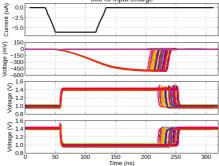

| 7.2  | Post-Layout Monte-Carlo Simulation Results (Min Q)                   | 70 |

| 7.3  | Post-Layout Monte-Carlo Simulation Results (Max Q)                   | 70 |

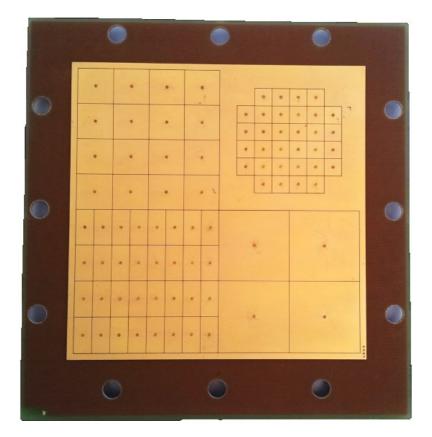

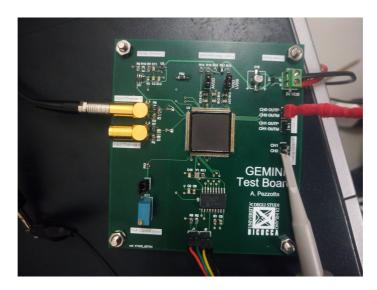

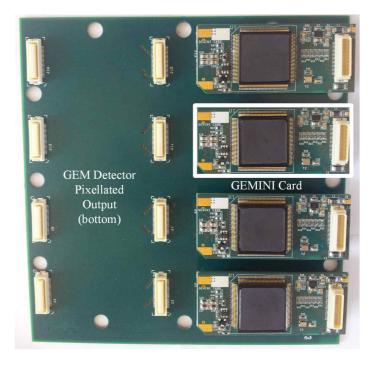

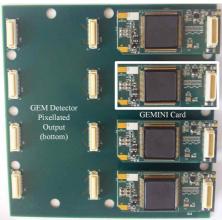

| 7.4  | GEMINI Test Board                                                    | 71 |

| 7.5  | GEMINI System                                                        | 71 |

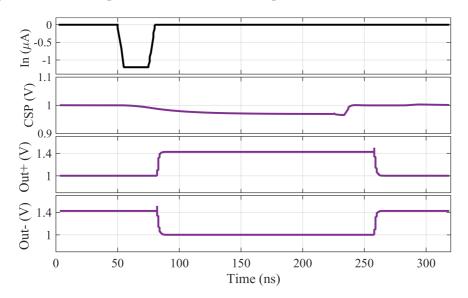

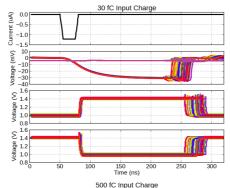

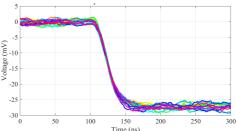

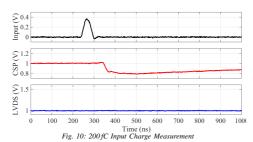

| 7.6  | GEMINI Signals for 30 fC Charge                                      | 72 |

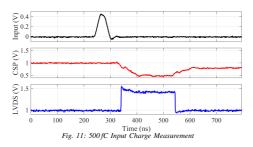

| 7.7  | GEMINI Signals for 500 fC Charge                                     | 72 |

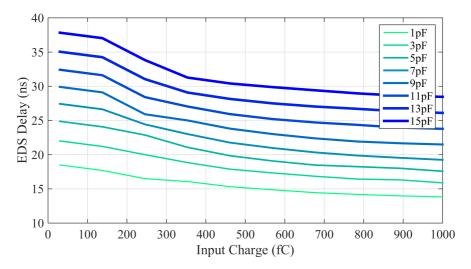

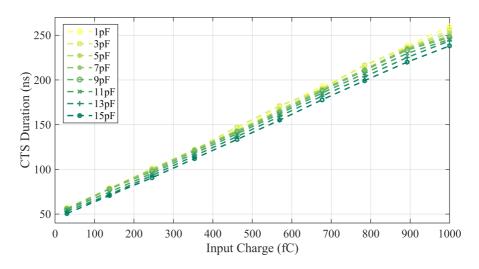

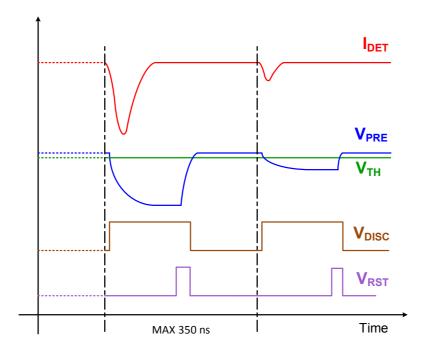

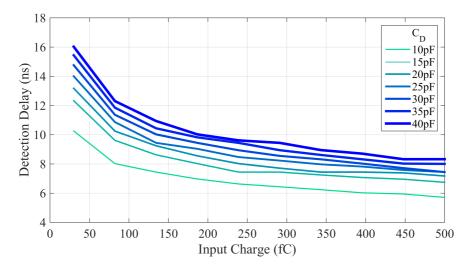

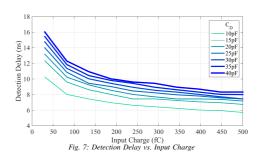

| 7.8  | Detection Delay vs. Input Charge       | 73 |

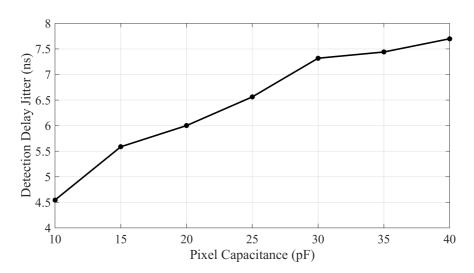

|------|----------------------------------------|----|

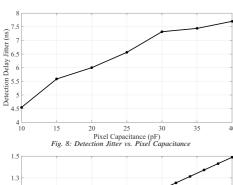

| 7.9  | Detection Jitter vs. Pixel Capacitance | 73 |

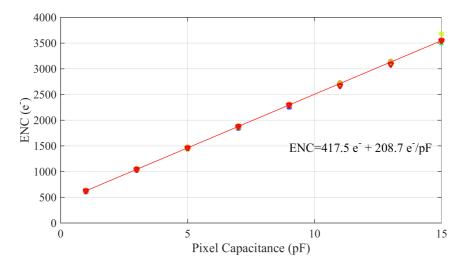

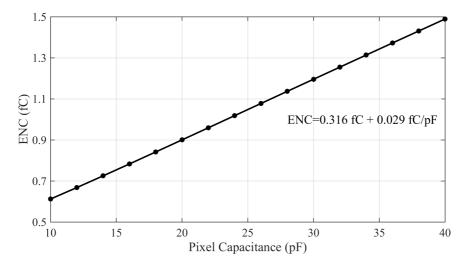

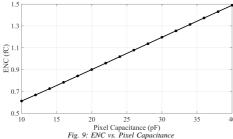

| 7.10 | ENC vs. Pixel Capacitance              | 74 |

## **List of Tables**

| 2.1  | Operational Amplifier requirements                       | 14 |

|------|----------------------------------------------------------|----|

| 2.2  | List of transistors dimensions                           | 22 |

| 2.3  | List of transistors dimensions                           | 26 |

| 2.4  | Resistive dividers values                                | 29 |

| 4.1  | PVT possible conditions                                  | 47 |

| 4.2  | PVT 81 corners with the corresponding resulting word     | 48 |

| 5.1  | GEMINI Operational Amplifier requirements                | 60 |

| 5.2  | List of GEMINI CSP Op-Amp transistors dimensions         | 60 |

| 5.3  | List of GEMINI Discriminator transistors dimensions      | 61 |

| 5.4  | List of GEMINI Calibration Block Parameters              | 63 |

| 10.1 | Comparison of GEMMA and GEMINI with the state of the art | 06 |

#

## Part I

**Preface**

#### 1

## Introduction

#### 1.1 Background and Motivations

In the wide world of particle detectors, gaseous ionization chambers are largely used due to their ability to make energy measurements and to discriminate various types of radiation. In last years a particular topology has emerged, named GEM (Gas Electron Multiplier) [1], developed at Gas Detector Development Group at CERN (European Organization for Nuclear Research) in 1997.

This detector has several advantages with respect to multi-wire proportional chambers, employed for similar applications. First of all, the manufacturing costs are much lower and, in principle, wide area GEM detectors are suitable for mass production. Instead, typical multi-wire chambers are very difficult to be assembled and more expensive, compared to GEMs. In addition, GEM detectors feature the capability to suppress positive ions, one of the most effective limiting factor in counting rate performance for this class of detectors.

On the other side this enhancement in the counting rate requires fast front-end electronics, enabling integrated circuit solutions.

Among the several advantages concerning GEM detectors design features, one of the key factors is that they can be easily built in different shapes and volumes. Standard fabrication techniques (such as lithography) has strongly increased the possible applications, reducing costs, and possibly improving the interfacing with CMOS integrated circuits.

Taking into account these aspects, several high-energy physics experiments exploit these detectors, especially for beam monitoring. One of the earlier employments was the COMPASS experiment at CERN [2], aiming at the study of hadronic structure and spectroscopy with high intensity muon and hadron beams, where GEMs were used as trackers.

Furthermore, they have been employed as neutron detectors with a Charge-Coupled Device (CCD) front-end system [3], within a radiographic system [4], as an X-Ray polarimeter [5] for astrophysics measurements, in ultra-fast soft X-Ray plasma diagnostics [6] and as a new-type photo-multiplier [7]. In addition to physics experiments, this detector has the great potentiality to be included in biomedical instrumentation, especially for diagnostics and monitoring [8].

The research in GEM detectors is pushing towards two mutual research branches. The first regards the detector physical/structure optimization, especially in the materials choice, in order to increase the signal gain, resolution and the count rate.

This brings to new architectures, including new gas mixtures and shape choices. A recent evolution has been named the Triple-GEM, realized at LNF (Laboratori Nazionali

4 Introduction

di Frascati) in Italy [9][10]. It consists in cascading three GEM foils in order to boost the detector signal gain. Furthermore, a particular mixture of gases ( $Ar/CO_2/CF_4$  45/15/40) improves time resolution.

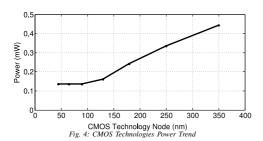

The second research branch is devoted to improve the front-end performance, using dedicated CMOS integrated solutions, suitable to sustain overall count rate (about 10<sup>6</sup> counts-per-second [10]), while reducing power consumption, and increasing system portability. In particular, the front-end here proposed allows to reduce power with respect to several circuits present in literature [11], enabling the possibility to include and optimize several input channels in the same silicon area (chip).

In the Triple-GEM readout system, an existent front-end has been adapted from other applications; this is the case of the CARIOCA [12], originally developed for Charge-Coupled Devices (CCDs) and included in a primary version of the Triple-GEM. But the limited count-rate and the relatively high power consumption has made the necessity of a dedicated readout system very real.

As a solution, the development of an ASIC (Application Specific Integrated Circuit) can afford several advantages with respect to other common solutions, i.e. PCBs [13]. In fact, the ultimate aim is the inclusion of a digital-based data elaboration in the front-end, greatly increasing performance and at the same time reducing the overall readout system complexity. Indeed, this fact can limit the inclusion of off-chip devices like FPGAs or standard micro-controllers.

Then, silicon implementation allows very dedicated circuital/system-level choices, optimizing overall readout performance while facing several project design issues, like large detector input parasitic capacitance and relatively low sensitivity.

#### 1.2 The GEM Detector

The detector for which the ASIC has been designed is the Gas Electron Multiplier (GEM), and belongs to the wide family of proportional counters. Provided that a more detailed description of the detector itself is not the main goal of this work, here a general overview of the device will be given.

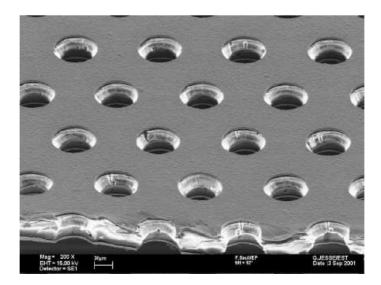

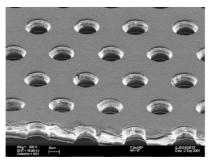

A typical GEM is made by a 50 µm thick kapton foil, with a copper clad on each side, perforated with a high-surface density of bi-conical channels. This foil is immersed in a particular mixture of gases. In figure 1.1 a SEM image of the foil is shown.

It can be realized in various geometrical configurations and also in great sizes. It's been introduced for particle detection recently [1], and this is one of the more active object of innovation in this field. Due to this, the development of a more dedicated front-end system is interesting, and in last years some configurations have emerged and will be explained in the next chapter.

The GEM can be used for different families of particle detection, such as neutrons, muons, electrons or gamma rays, with very few modifications to the basic structure (e.g. adding a conversion cathode for uncharge particles).

#### 1.2.1 Basic principles of functioning

The main process of signal generation inside the detector is the same of a typical gas ionization chamber. In fact, a charged particle entering the active volume, if energy

Figure 1.1: SEM image of the GEM foil (from CERN GDD Group)

constraints are respected, ionizes an atom of the gas and creates an electron-ion pair. In presence of an electric field, this two carriers will tend to move towards the anode and cathode respectively. If the intensity of this electric field is high enough to overcome a specific threshold, the kinetic energy of the electrons will increase up to ionize an other atom, creating other active carriers. Thus, a greater signal will be produced at the anode, although keeping the proportionality between deposited energy and the amount of charge at the anode. This fact enables the possibility to make a spectroscopic analysis of the incident particles.

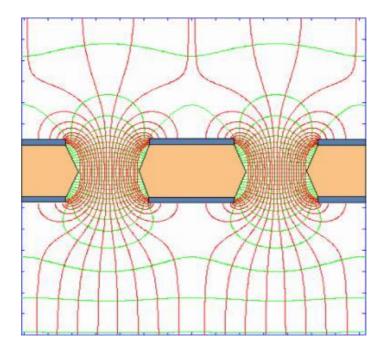

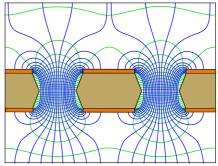

The great innovation of the GEM is that the high electric field necessary to multiply the carriers is generated in the foil channels (typically with a 70  $\mu$ m diameter) by applying a bias voltage between each of the two copper clads. Therefore, a lower bias can be applied in order to obtain the same electric field intensity of conventional proportional detectors (approximately  $10\,\text{MV/m}$ ). Into channels, as a consequence, an electric field similar to that shown in figure 1.2 will establish.

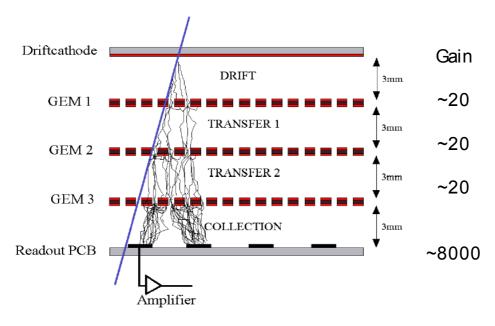

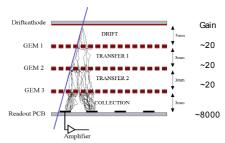

It's in this region that the multiplication process takes place. In a typical configuration, each foil has a multiplication factor in the order of 20. In order to achieve further signal amplification, more GEM foils can be added to the chamber (three foils, as shown in figure 1.3, reach a 8000 multiplication factor).

Other key advantages in employing GEM detectors are the possibility to get information about the position of particle interaction as a consequence of this structure, and to make time-of-flight measures thanks to its very little characteristic time of detection. The enhanced adaptivity of the GEM is the key of its success in particle detection employment; it can be tuned for several applications changing its geometrical configuration or the materials of its components.

A typical complete configuration is shown in figure 1.4.

6 Introduction

Figure 1.2: Electric field lines in a GEM (from CERN GDD Group)

Figure 1.3: Structure and gain of a GEM (courtesy of F. Murtas)

Figure 1.4: GEM typical configuration (courtesy of F. Murtas)

#### 1.2.2 Recent Developments: BANDGEM

New high count rate detectors are needed for future spallation neutron sources where large areas (several  $m^2$ ) and high efficiency (> 50%) detectors are envisaged.

In this framework, GEM is one of the explored detector technologies since they feature good spatial resolution (< 0.5 cm) and timing properties, have excellent rate capability (MHz/mm<sup>2</sup>) and can cover large areas (some m<sup>2</sup>) at low cost.

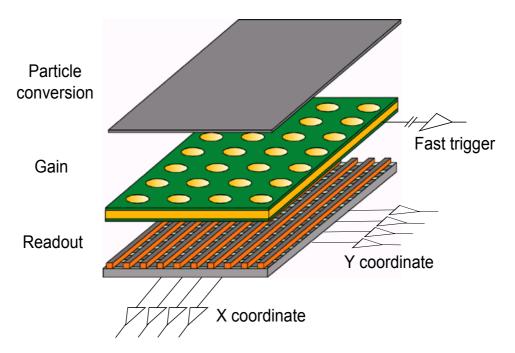

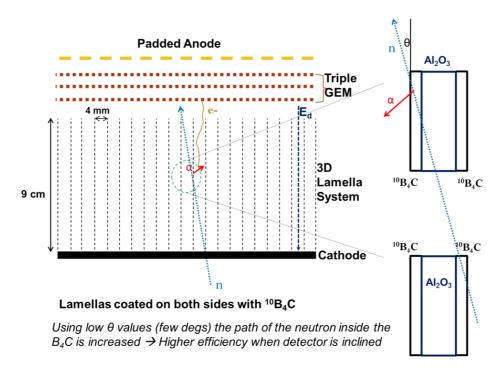

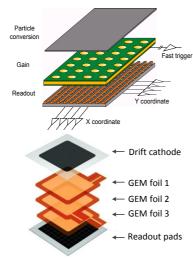

Thus, the BANDGEM (Boron Array Neutron Detector) approach (Figure 1.5), a 3D geometry for the neutron converter cathode, was developed expecting to provide an efficiency > 20% in the wavelength range of interest for Small-Angle-Neutron-Scattering instruments.

A system of thin lamellas (250  $\mu$ m) of dielectric material coated with 1  $\mu$ m layer of  $^{10}B_4C$  has been built and positioned in the first detector gap, orthogonally to the cathode

By tilting the lamellas system with respect to the beam, there is a significant increase of effective thickness of the borated material crossed by the neutrons. As a consequence, both interaction probability and detection efficiency are increased.

This detector is aiming to replace <sup>3</sup>He tubes for neutron detection. In fact, although their performance (in particular the high energy resolution and the high efficiency in charge collection), the availability of <sup>3</sup>He has become prohibitive, with extremely high costs, together with the bulky structure of the detector itself.

8 Introduction

Figure 1.5: The BANDGEM configuration (courtesy of G. Croci)

#### 1.3 The State-of-the-Art on Readout Electronics

One of the most commonly used ASIC for GEM detector readout is the CARIOCA (CERN And RIO Current-mode Amplifier), which is an octal amplifier shaper discriminator with baseline restoration, dedicated to Multi Wire Proportional Chambers (MWPC), and later re-adapted for GEM detectors [12]. It is developed in 250 nm CMOS technology, that operates at 2.5 V. The CARIOCA amplifier is developed in the current-mode approach, that is attractive for fast circuits. The chip has to amplify, shape and discriminate the current signal induced on the wire chamber electrodes. Another recent development is the GASTONE64 chip [14]. The GASTONE64 (GEM Amplifier Shaper Tracking ON Events) is a low-noise low-power mixed-signal ASIC designed to host 64 channels to readout a cylindrical GEM detector. Each channel is made of a charge sensitive preamplifier, a shaper, a discriminator and a monostable. Digital output data are transmitted via serial interface at 100 Mbit/s data rate. The chip has been designed in 350 nm CMOS process.

# Part II GEMMA Prototype

#10

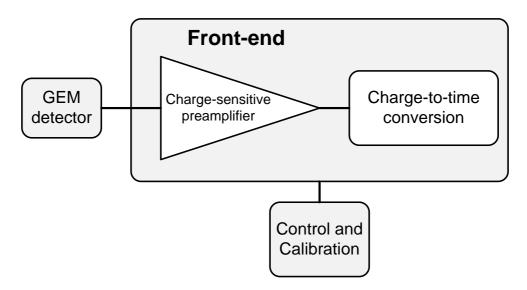

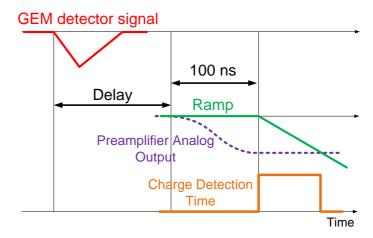

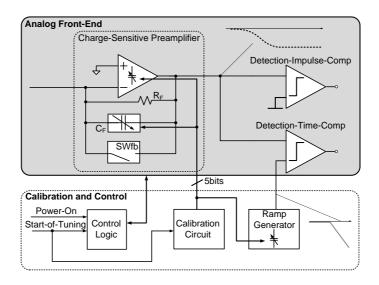

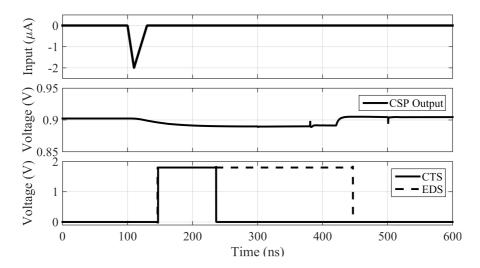

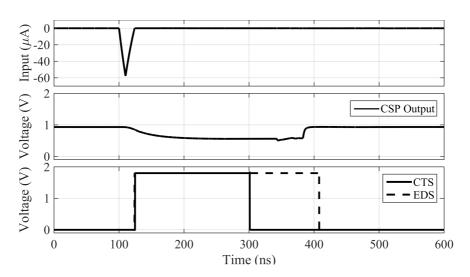

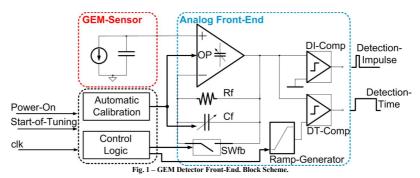

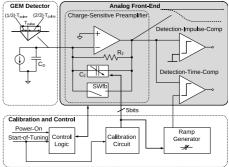

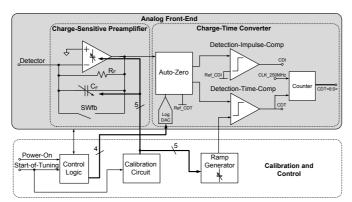

The block scheme of the GEMMA front-end channel is presented in figure 2.1. It consists of three main blocks, that is the charge sensitive preamplifier, the charge-time conversion block and the calibration/control block. The front-end in figure 2.1 has been designed specifically for negative charged particles. Its ultimate aim is to measure the arrival time (Event-Detection-Signal, EDS) and the amount of charge generated by the GEM detector (Charge-Time-Signal, CTS).

Figure 2.1: GEM detector front-end, block scheme

#### 2.1 GEM Detector signal modeling

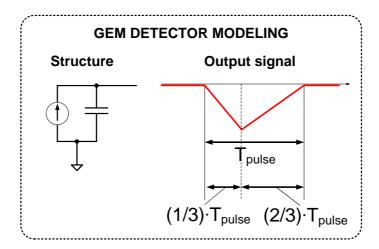

The input charge time-duration enters into a  $30\,\mathrm{ns}$  up to  $100\,\mathrm{ns}$  range [12]. The input pulse shaping is reported in figure 2.2, and it has been considered to feature different rise and fall time, respectively as 1/3 and 2/3 of the total time duration [10]. The input charge can assume values from  $30\,\mathrm{fC}$ , corresponding to a MIP (Minimum Ionization Particle), up to  $1\,\mathrm{pC}$ .

#### 2.2 **GEMMA Signals**

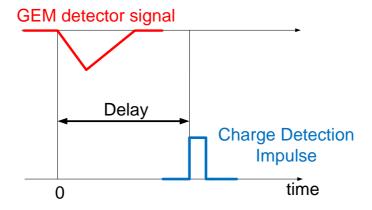

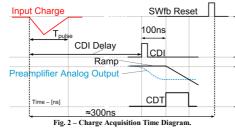

With reference to figure 2.3, EDS is available when an input charge higher than 30 fC is detected by the front-end. This signal is generated by a comparator, named for clearance EDS-Comp. This signal has to be generated within a 30 ns time interval after

Figure 2.2: GEM detector modeling

the 0 time in figure 2.3.

Figure 2.3: Event detection impulse (EDS) diagram

Contemporaneously with the EDS impulse, the preamplifier starts to integrate the GEM signal, and the CTS measure starts, as the output of another comparator named *CTS-Comp*. After 100 ns, a negative constant-slope ramp starts and the output of the CTS-Comp remains high until the preamplifier output voltage crosses the ramp. The produced pulse, shown in figure 2.4, contains information about the amount of charge at the front-end input, because its time duration is directly proportional to the input detector charge.

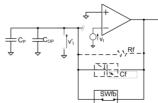

#### 2.3 Detection Chain

The signal coming from GEM detector goes through the Charge-Sensitive Preamplifier (CSP), composed by a passive feedback net  $C_F$ - $R_F$ , the reset switch SWfb, and the single-ended Opamp, shown in figure 2.5.  $R_F$  (set very high, about  $1\,\mathrm{M}\Omega$  maintains

2.3 Detection Chain 13

Figure 2.4: CTS diagram

the Opamp input/output operating point. By closing SWfb it is possible to discharge the  $C_F$  capacitor and restore the common-mode voltage at the opamp input/output node. Such reset operation is required every time a EDS pulse occurs, and once the CTS signal is available.

Figure 2.5: GEMMA Front-end complete scheme

Basically the front-end here presented is able to perform a charge vs. time conversion. The ramp signal for voltage vs. time conversion is generated by a proper Ramp-Generator circuit, whose implementation is based on a constant current charging a capacitor during a fixed time. A very precise external current has to be provided, while variable capacitors are tuned by the calibration circuit (explained in detail in

section 2.5) in order to guarantee a very precise ramp signal, within a  $\pm$  5% tolerance.

#### 2.4 Front-end Design: Charge Sensitive Preamplifier

#### 2.4.1 Operational Amplifier

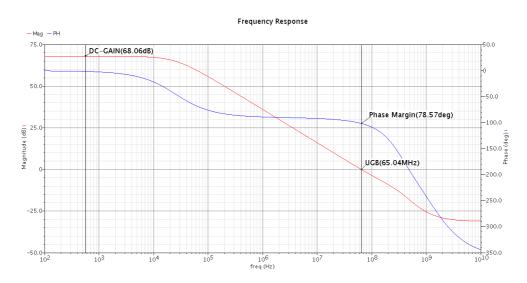

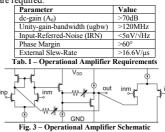

Due to the virtual ground principle at the Operational Amplifier input, GEM detector parasitic capacitance does not affect significantly the charge-to-voltage conversion, implemented by the CSP. For this reason system-level analysis has demonstrated at least 60 dB of DC-gain are needed for Operational Amplifier in figure 2.5.

Moreover, taking into account a possible DC-gain drop, due to PVT and aging, 70 dB DC-gain has been required. Since rising time should be about 1/3 of the input signal total time duration (100 ns), output slew-rate for the Operational Amplifier is about 16.6 V/ $\mu$ s. At the same time for Equivalent-Noise-Charge (ENC) performance, Input-Referred-Noise (evaluated as spot noise on the middle of preamplifier bandwidth) should be lower than  $10\,\mathrm{nV}/\sqrt{Hz}$ . Unity gain bandwidth requirements are then fixed by rise/fall time. A resume of the most important Op-Amp requirements is reported in table 2.1. Notice that for stability reasons at least a 60° Phase Margin is required.

| Parameter                  | Value                        |  |  |

|----------------------------|------------------------------|--|--|

| DC-gain (A <sub>0</sub> )  | $> 70 \mathrm{dB}$           |  |  |

| Unity-Gain-Bandwidth (UGB) | > 120 MHz                    |  |  |

| Input-Referred-Noise (IRN) | $< 10 \mathrm{nV}/\sqrt{Hz}$ |  |  |

| Phase Margin               | > 60°                        |  |  |

| External Slew-Rate         | > 16.6 V/µs                  |  |  |

Table 2.1: Operational Amplifier requirements

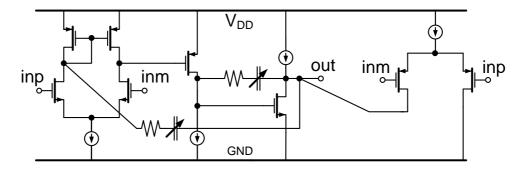

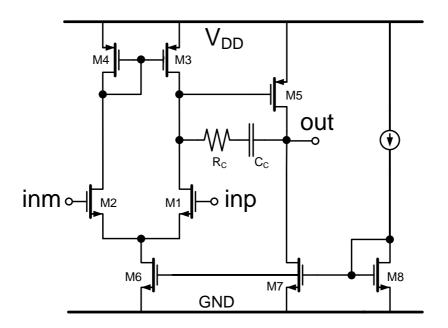

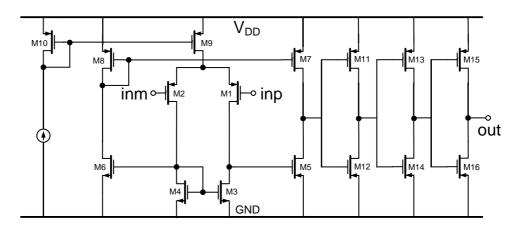

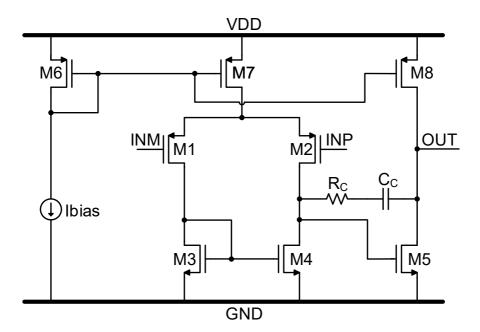

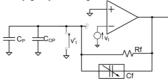

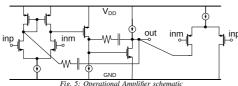

The charge-sensitive preamplifier should be designed with a very high open loop gain in order to obtain a very low input impedance. The solution adopted in this work is a 3-stage Op-Amp with Nested Miller Feed-Forward compensation technique [15]. In particular, 70 dB DC-gain and 120 MHz minimum unity gain bandwidth requirements make the Op-Amp design very challenging. Single Miller compensation is here not sufficient, because three gain stages are needed to perform the minimum required DC-gain of 70 dB. Feed-Forward compensation appears the most reasonable solution, in order to guarantee stability (at the cost of smaller power increasing due to the feed-forward path, see figure 2.6).

#### 2.5 Front-end Design: Calibration Circuit

#### 2.5.1 Calibration circuit general description

The CMOS integration process, due to its nature, brings to a statistical variation of all parameters involved in a circuit [16]. These parameters are related to transistors, resistors, capacitors, and also the silicon wafer. These variations are particularly relevant, and the designer has to take them into consideration because they affect the

Figure 2.6: Operational Amplifier schematic

global performance.

In detail, this project bases its functioning on capacitors, included in the preamplifier as feedback capacitor and Miller compensation capacitors.

It has been demonstrated that the capacitors mean standard variation due to the integration process can reach 40% w.r.t. the nominal value [17]. This fact can affect seriously the front-end performance.

In this design indeed, the requested precision of capacitance values is 5%. This fact is due to three critical points. The first two regard the preamplifier feedback capacitor ( $C_F$ ) value, included into the integration constant, and responsible of the loop gain, and so of the Op-Amp phase margin. The third, linked to the Miller compensation capacitor values, is responsible of the preamplifier Op-Amp stability.

The solution to this issue consists in designing an automatic calibration circuit, which tunes the capacitors value directly on-chip and automatically, including only a precise current reference (given as a chip input) and a stable clock signal.

The calibration algorithm is made by three main steps: sensing, calibration and convergence.

#### Sensing

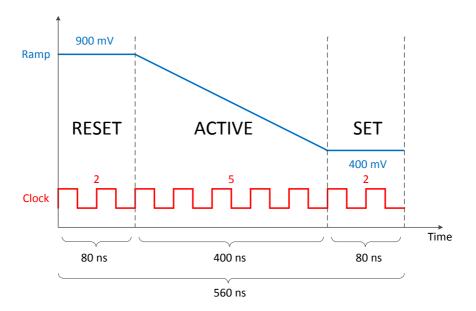

The sensing procedure is started at the algorithm beginning. It consists in evaluating the effective capacitance implemented value. Namely, the sensing is made by generating a linear descending ramp into a determined time interval, established in multiples of the clock signal cycles. Indeed, assuming

$$I = \frac{\Delta Q}{\Delta t} = \cos t. \tag{2.1}$$

hence

$$\Delta Q = C \cdot \Delta V \Longrightarrow \frac{\Delta V}{\Delta t} = \frac{I}{C}$$

(2.2)

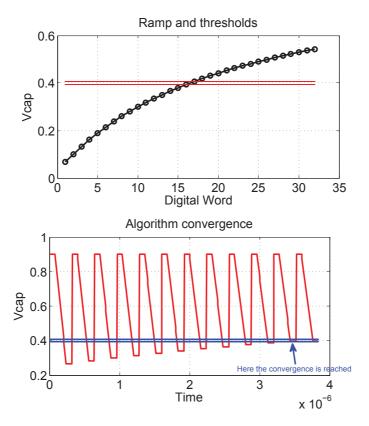

So, a fixed constant current charging a capacitor in a determined interval of time will produce a precise bias voltage. The produced ramp is shown in figure 2.7.

The sensing procedure will be made in the SET phase. Reference bias values, time duration and clock frequency have been chosen according to a MATLAB® simulation.

Figure 2.7: The calibration ramp in nominal conditions

In equation 2.2, once fixed the starting bias level, the nominal capacitor value and the charging current (respectively  $900\,\text{mV}$ ,  $1.8\,\text{pF}$  and  $2.25\,\mu\text{A}$ ), it is possible to calculate the clock frequency or the arriving bias voltage. In fact the ramp duration has to be a multiple of clock signal, because all the analysis is made digitally. Here a 5 times the clock period ramp time has been chosen. With a  $12.5\,\text{MHz}$  clock, the ramp lasts  $400\,\mu\text{m}$  and reaches a  $400\,\text{m}$ V bias.

#### Calibration

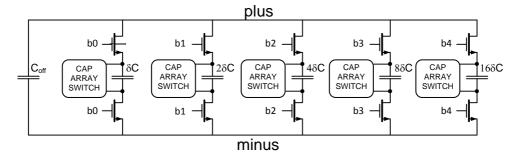

The basic concept behind its logic is the checking of resulting ramp bias and to make the capacitance value to change accordingly. So, a binary-weighted digital programmable capacitor array has been implemented, which allows to select a specific value with a digital word. The calibration precision so will depend on the number of implemented capacitors, acting as bits.

Let be  $C_{nom}$  the nominal value of the capacitance, N the number of array bits,  $\Delta C$  the maximum relative variation of the capacitance value due to integration technology. Therefore, the possible combinations of the capacitance value are  $2^N$ . The minimum value  $C_{min}$  and the maximum  $C_{max}$  will be

$$C_{\min} = C_{\text{nom}} \cdot (1 - \Delta C) \tag{2.3}$$

$$C_{\text{max}} = C_{\text{nom}} \cdot (1 + \Delta C) \tag{2.4}$$

Hence, the difference between two consecutive values and so the maximum error  $\epsilon$  with respect to the nominal value is simply

$$\epsilon = \frac{C_{\text{max}} - C_{\text{min}}}{2^{N}} = \frac{2 \cdot \Delta C}{2^{N}} = \frac{\Delta C}{2^{N-1}}$$

(2.5)

Once the capacitance value maximum variation is known, fixing the number of bits corresponds to fix the maximum error.

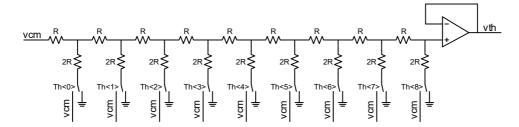

After that, following the calculations made in equations 2.3 to 2.5 and the maximum variation of the capacitance fixed ( $\Delta C$  in equation 2.5), the MATLAB<sup>®</sup> program calculates the offset capacitor of the array as  $C_{\min}$  and makes a relation between the bit code and the value of capacitance in the array. Choosing the bit code corresponding to nominal capacitance, named  $N_{\rm init}$ , the program calculates also the two thresholds for the comparators, respectively  $V_{\rm th_H}$  and  $V_{\rm th_L}$  as follows:

$$\begin{split} V_{\rm th_L} &= V_{\rm reset} - \frac{T_{\rm charge} \cdot I_{\rm ref}}{C(N_{\rm init})} \\ V_{\rm th_H} &= V_{\rm reset} - \frac{T_{\rm charge} \cdot I_{\rm ref}}{C(N_{\rm init} + 1)} \end{split} \tag{2.6}$$

$$V_{\text{th}_{\text{H}}} = V_{\text{reset}} - \frac{T_{\text{charge}} \cdot I_{\text{ref}}}{C(N_{\text{init}} + 1)}$$

(2.7)

#### Convergence

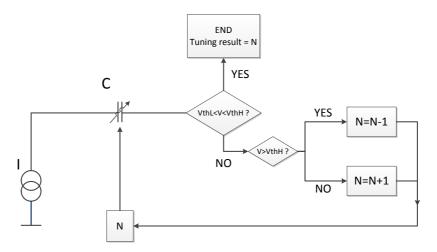

The setting of array bits changes until the bias variation in a determined number of clock cycles is into the desired window, as shown in figure 2.8.

Figure 2.8: Algorithm of the tuning process

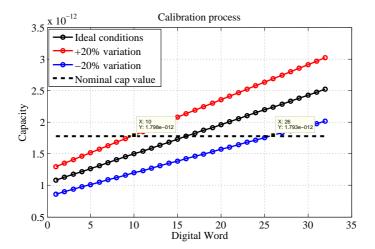

In figure 2.9 the digital word vs. capacitance relation is shown in the nominal case, and in the case of 20% positive and negative variation due to the integration process. In figure 2.10 the MATLAB® simulation results are shown, including a simulated convergence in the case of -20% capacitance variation (the second plot).

#### Schematic choice

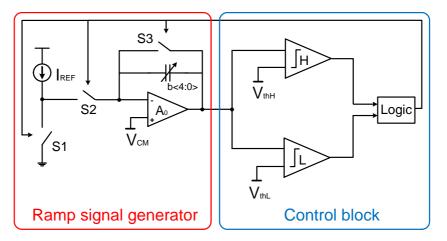

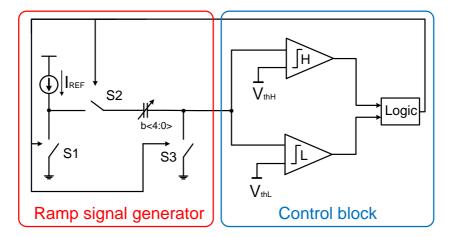

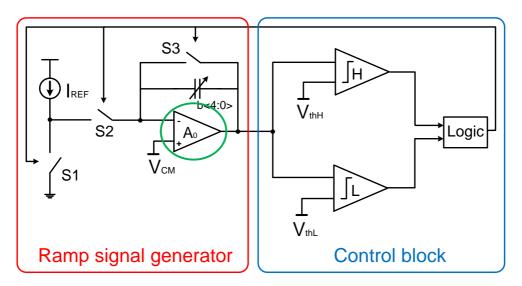

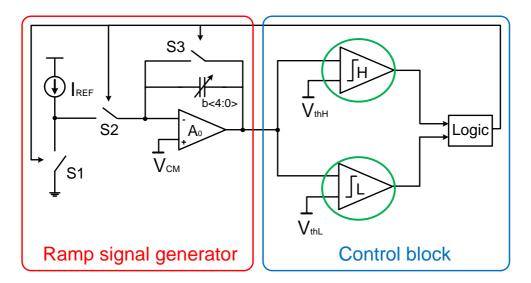

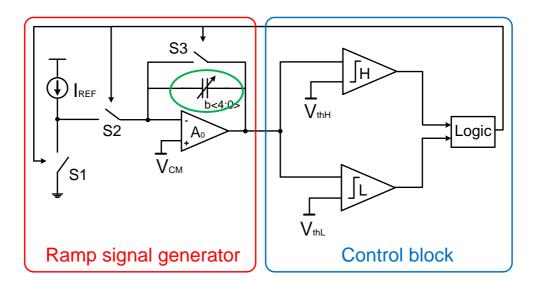

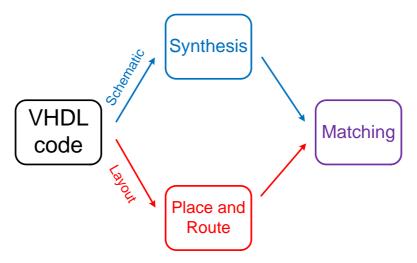

The tuning machine, as shown in figure 2.11, is composed by two main blocks: the analog ramp generator and the digital controller.

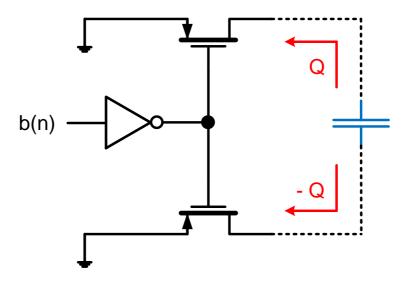

Inside the first block, a constant current charges a digital programmed array of N capacitors put in feedback of an operational amplifier. So, by opportune clock phases generated by the digital part, a series of switches generate a ramp signal. This

Figure 2.9: The capacitor values related to the digital words

Figure 2.10: Matlab simulation results

configuration has been preferred to a simple charged capacitor as shown in figure 2.12.

Figure 2.11: Low-level diagram of the tuning machine

Figure 2.12: Alternative low-level diagram of the tuning machine

In fact, in this last configuration, the Op-Amp allows to drive a load capacitance, and guarantees an uncoupling with respect to the rest of the circuit. Moreover, the ramp in first (and used) configuration is descending, while in the second is raising.

#### 2.5.2 Calibration Analog Section

In this chapter the analog components of the calibration circuit will be described. Although the whole tuning machine is a perfect example of a mixed-signal circuit, because the digital and analog worlds are strictly working together, the description of each one will be separated.

#### **Operational Amplifier**

The operational amplifier implemented here has not a real amplifying behavior, but is fundamental to maintain the ramp linear. In fact, the virtual ground principle

Figure 2.13: Operational Amplifier

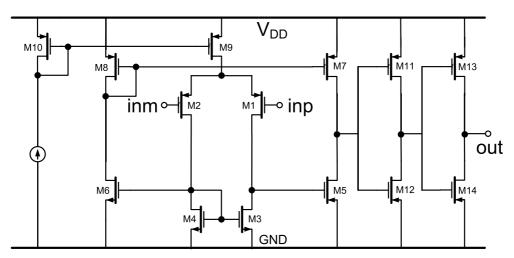

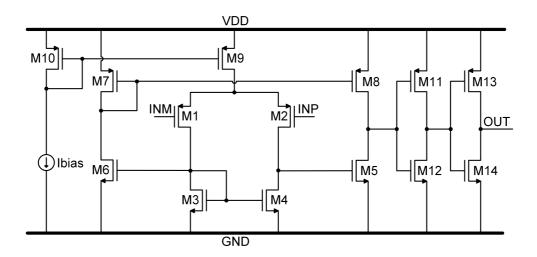

states that if an Op-Amp has a very high open-loop gain, and it has a feedback, the difference between its input terminals is negligible. So, the input current is maintained constant. Moreover, the use of an Op-Amp allows to drive an output load, in this specific case represented by the two comparators inputs. The Op-Amp schematic is shown in figure 2.14.

Figure 2.14: Op-Amp schematic