## Universita' degli Studi di Milano-Bicocca

PhD in Physics and Astronomy (Cycle 35) - Applied Physics and Electronics

# High Frequency Buck Converter for Automotive Current Source Applications

Candidate: Tutor:

Albino Pidutti Prof. Andrea Baschirotto

Student Number: Supervisor:

MAT. 854432 D.I. Paolo Del Croce

A.Y. 2021/2022

Coordinator: Prof. Stefano Ragazzi

Since, during this PhD, I have always appreciated the dedication to profession and commitment shown by all the health staff of the nephrology departments of the "San Daniele del Friuli Civil Hospital" and the "Santa Maria della Misericordia Hospital" in Udine, I would like to dedicate them this PhD.

I also want remember those who donated us a normal life before they leave us,

...

because Humanity is a Big Team connected in the past, present and future.

# Acknowledgements

I would like to thanks Infineon and University of Milano Bicocca who gave me the opportunity to do this PhD. In particular Ing. Paolo Del Croce and Professor Andrea Baschirotto for their advice and collaboration.

Thanks to Günter and Mike for layouts.

Thanks to Paola, whose cheerfulness supported me during this period.

Thanks to my young PhD colleagues, especially Francesco and Marcello, for their help and the breath of fresh air they brought.

And a big thanks to all those who in various ways have shared this work.

# Abstract

The advent in the 1980s of discrete high-voltage DMOS with more manageable threshold voltage values and consequent ease of drive, speed of response, and simplicity of construction compared to bipolar devices, led to an increased demand for power supplies for the increasingly popular electronic circuits. This has generated a growing interest in DC-DC power supplies over linear ones.

The big advantage of DC-DC power supplies, apart from their relative simplicity, is their efficiency, allowing them to easily achieve values above the 90%. These efficiencies represented a significant improvement over the linear ones dependent in the first approximation on the ratio between output and supply voltage.

Furthermore, it quickly became apparent that increasing the switching frequency would linearly reduce the size of DC-DC components, smaller Printed Circuit Boards (PCBs). and consequently reduced costs. The frequency increase for Power DC-DCs ( $\geq 1A$ ) has grown steadily, but slowly, and only in recent years frequency have reached values in the order of MHz.

In the automotive field, electrical and electronic devices are powered by the battery, whose typical voltage with the engine running is around 14 V, but experiences transient voltages that can vary between 4.5V (e.g. during cold starting) to over 30V (during load-dumping).

In addition, new functions such as start & stop, increase the frequency of such transients with heavier electronic device operating requirements. This requires off-battery power ICs to function under more critical operating conditions in order to reliably supply the entire vehicle.

In the automotive industry, we see a continuous growth in the use of electronic equipment for both safety and entertainment, for instance lane change warning, sleep sensors, proximity sensors, touch screen displays, cameras and so on. In the lighting field there has been a rapid and progressive transition from incandescent lamps to xenon to LEDs for both exterior and interior lighting as they perform better in terms of energy efficiency than conventional ones. However, due to their electrical characteristics these systems must be supplied with current controlled equipment.

DC-DC converters offer a simple and efficient way to supply the recent electronics loads. In addition, DC-DC power supplies make it possible to effectively meet many safety requirements in modern automobiles. In fact, it is absolutely necessary that hazard lights, headlights and brake lights maintain their functionality under all conditions, especially during cold starting, when the battery voltage reaches very low values. Consequently, DC-DC converters, Buck, Boost and Buck-Boost, for automotive applications are of great interest due to their ability to quickly adapt to different supply voltages as well as their high efficiency. Finally, interest in monolithic solutions has been growing in recent years, and the integrated circuit companies with their BCD (Bipolar, CMOS, Dmos) technologies are very active in this field.

Furthermore, increasing the switching fequency means cheaper, smaller and more manageable DC-DC converters, which are welcome features not only in the automotive sector. This is why both academia and industry, increasingly interconnected, are proposing new technological and circuit solutions.

In this work, my goal is to develop a buck converter with a switching frequency in the order of a few MHz and an output current of a few A using the automotive-qualified BCD technologies available in our group and implementing circuit solutions to reduce discrete components with the aim of reducing costs and volumes.

Our BCD technologies are suitable for a high degree of integration as they enable the integration on a single chip of DMOS power transistors, current sense, bootstrap diodes, control logic and diagnostics.

Since the automotive field requires not only efficiency but also reliability and safety, mature and proven technologies are preferred. Moreover, since development costs are already amortised, they are less expensive, so that the increasingly pressing demand for low cost is also met.

To tackle this work, a literature search was carried out regarding both the latest innovations and the offers available on the market.

Three buck converters have been developed using new innovative solutions with frequencies of 1MHz, 4MHz and 10MHz. The 4MHz Buck Converter is currently the most interesting one for our market, while the 10MHz buck has an investigative role.

In addition the work carried out led to four patent applications.

# Contents

| 1 | Cor | stant Current Buck Converter for Automotive Current Source     |

|---|-----|----------------------------------------------------------------|

|   | App | olication                                                      |

|   | 1.1 | Introduction                                                   |

|   | 1.2 | DC-DC Converters, Basic Topologies Overview                    |

|   | 1.3 | First Investigation                                            |

|   | 1.4 | Design Target                                                  |

|   | 1.5 | Design Guidelines                                              |

|   | 1.6 | Integrated Development                                         |

| 2 | Buc | ek Converter Architecture                                      |

|   | 2.1 | Floating Control Logic                                         |

|   | 2.2 | Block Diagram                                                  |

|   | 2.3 | Fixed $t_{OFF}$                                                |

| 3 | Sta | rt and Bootstrap Diode Blocks                                  |

|   | 3.1 | Start Block                                                    |

|   | 3.2 | Bootstrap Diode Block                                          |

| 4 | Aux | kiliary Blocks 21                                              |

|   | 4.1 | Introduction                                                   |

|   | 4.2 | Supply Block                                                   |

|   | 4.3 | Bandgap Block                                                  |

|   | 4.4 | UVSD - (Under Voltage Shut Down) Block                         |

| 5 | Cor | ntrol Driver 29                                                |

|   | 5.1 | Introduction                                                   |

|   | 5.2 | High Speed Driver                                              |

|   | 5.3 | Driver Control Simulations                                     |

| 6 | Cur | rent Sense and Control Logic - PVT Simulations 37              |

|   | 6.1 | Current Sense                                                  |

|   | 6.2 | Control Logic                                                  |

|   | 6.3 | 10 MHz Buck Converter Simulations                              |

|   | 6.4 | 4 MHz Buck Converter PVT (Process, Voltage, Temperature) Simu- |

|   |     | lations                                                        |

| 7 | Lay | out 45                                                         |

|   | 7 1 | Buck Converters Layout 45                                      |

| IV | CONTENTS |

|----|----------|

|    |          |

| 8  | PCB Design                          | <b>49</b> |

|----|-------------------------------------|-----------|

|    | 8.1 Introduction                    | 49        |

|    | 8.2 PCB Simulations and Development | 50        |

|    | Appendix                            | 53        |

|    | Patents                             | 61        |

|    | Conclusions                         | 97        |

| Bi | ibliography                         | 101       |

# Chapter 1

# Constant Current Buck Converter for Automotive Current Source Application

### 1.1 Introduction

The global demand for energy savings is pushing for solutions other than traditional ones, and obviously the automotive sector is also playing its part. In cars, the source of electricity is the battery, which provides a voltage around 14V when the engine is running, while electronic equipment present in increasing quantities require supply voltages ranging from 3V to 6V, just think of the ever-increasing number of entertainment devices like parking cameras, proximity sensors and so on. This requires an increasing number of voltage adapters.

Conventional linear power supplies have a low efficiency, in first approximation proportional to the ratio  $V_{out}/V_{in}$  (20% - 40%), they are therefore increasingly being replaced by DC-DC converters that easily reach efficiencies of 90% and more. An emblematic case are both outdoor and indoor lights that are switched from battery-powered incandescent lamps to LED lamps. These are supplied with a constant current, so that the voltage across them varies greatly with temperature. At their ends they typically show voltages between 1.5 and 3.5 V. For LED, the DC-DC supplier is the ideal solution. While typically low-power indoor lights are usually group-powered, the much more powerful outdoor lights each require a dedicated DC-DC power supply.

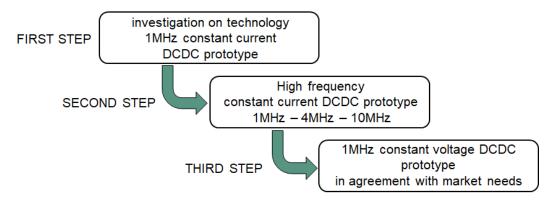

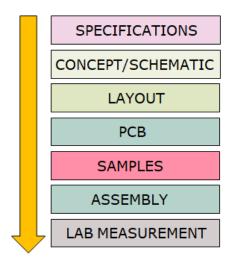

Our Body Power division, despite its long tradition in ballasts for incandescent lamps and its enviable product portfolio, is looking with great interest at DC-DC converters [1] [2] [3] [4] [5] [6] [7] [8]. It has therefore initiated a collaboration plan with the University of Milan Bicocca, which, simplifying, we can divide into three parts (Figure 1.1). The first step is to study the suitability of the proprietary BCD technology for the production of DC-DC converters and to design a 1MHz constant current Buck power supply. The second phase is to test the behaviour of Buck's high-frequency constant-current power supplies. Finally, with the third part, we want to build a prototype with constant voltage output and characteristics closer to market requirements. With the present work we deal with the second part, the target is to design three Buck converters with 3A constant output current operating at 1MHz, 4MHz and 10Hz. The main focus is on Buck at 4 MHz.

Figure 1.1: Development Plan in collaboration with the University of Milano Bicocca

## 1.2 DC-DC Converters, Basic Topologies Overview

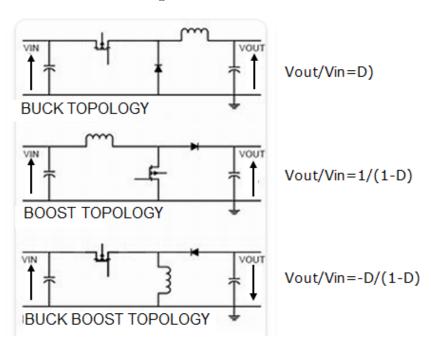

With the increasing use of DC-DC converters, many topologies have been derived, but all can be developed from the three basic topologies Buck, Boost, Buck-Boost (Figure 1.2) [9].

- Buck:  $V_{out}/V_{in} = D$ . The output voltage is always lower than the input voltage. Ideal for the automotive sector because many loads must be supplied at lower voltages.

- Boost:  $V_{out}/V_{in} = 1/(1-D)$ . The output voltage is always higher than the input voltage. There are some automotive applications in which it is used.

- Buckboost  $V_{out}/V_{in} = -D/(1-D)$ . The output voltage can be either higher or lower than the input voltage, but has inverted polarity. This is why it is often used in many sectors with an inverting transformer. It is not used in automotive.

Figure 1.2: DC-DC Base Topologies

In automotive the Buck converter is suitable for driving electronic loads as the

requested supply voltage is  $3 \sim 6 \text{ V}$ .

## 1.3 First Investigation

With this work, using the automotive qualified technologies available to our group, the aim is to make the Buck converter more economical and manageable. This can be achieved by increasing the integration level and by increasing the switching frequency to reduce the size of the discrete components in order to obtain smaller PCBs.

We can choose between two available BCD technologies that are similar in components, both of which allow the integration of a very efficient power DMOS, current sensing and bootstrap diode, but one allows through additional process steps the integration of large capacitors, even several nF, this feature allows on-chip bootstrap capacitor (I denote this technology by BCD-cap, the other simply by BCD).

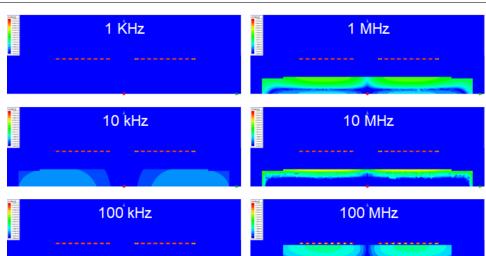

BCD-cap was the first choice, and I also wanted to check whether it made sense to integrate an inductance of a few tens of nH into the silicon. Several articles in the literature deal with this topic [10] [11]. I thought of an elliptical structure Figure 1.3 and with the help of the process group, some simulations were carried out. Since the real inductance is associated with parasitic components, series resistance, conductance and capacitance in parallel, it is important to assess the effect of frequency on deterioration of the desired inductance.

Figure 1.3: simulated spiral inductance - two elementary cell

The results of simulations at different frequencies (1KHz, 10KHz, 100KHz, 1MHz, 10MHz and 100 MHz) are shown in Figure 1.4 and Figure 1.5.

The simulations show that the losses caused by Eddy currents affect both the underlying silicon and the leadframe, in the latter, being metallic, the losses are already relevant at relatively low frequencies. Table in figure 1.6 shows that at 100 MHz the inductance is reduced from 71.4nH to 48.2nH.

In [12] to confine the magnetic field is poposed two layer spiral inductor, one in the upper and one in the lower face, thus reducing losses in the lead-frame.

Regarding the volume of silicon underlying the inductance, I proposed dividing the silicon into small isolated volumes by means of trenches, solution borrowed from the ferrite magnetic cores used in the high-frequency transformers [13].

This solution suggested a patent proposal.

4

Figure 1.4: Simulated Losses at Several Frequencies - 1KHz, 10KHz, 100KHz, 1MHz, 10MHz, 100MHz

Figure 1.5: Losses Simulated at 100MHz

| Coil RLO | parameters | at | 100 | MHz     |

|----------|------------|----|-----|---------|

| COLLINE  | parameters | aı | 100 | IVII IZ |

| Case                                        | R <sub>DC</sub><br>(Ω) | R<br>(Ω) | L<br>(nH) | Q    |

|---------------------------------------------|------------------------|----------|-----------|------|

| Si <u>lossy</u>                             | 0.53                   | 6.4      | 47.5      | 4.6  |

| Si lossless (active and bulk)               | 0.53                   | 1.4      | 48.2      | 22.0 |

| Si lossless, wo die<br>attach and leadframe | 0.53                   | 1.7      | 71.4      | 25.7 |

Eddy current loss in Si significantly deteriorates coil's quality (22.0  $\rightarrow$  4.6 @ 100 MHz) Eddy currents in leadframe below the coil reduce coil's inductance (71.4 nH  $\rightarrow$  48.2 nH @ 100 MHz)

Figure 1.6: degradation of inductance at 100 MHz

Despite interesting developments, I had to abandon ongoing investigations as management opted to optimise development efforts and focus them in one direction by allowing only one development testchip for commercial products in BCD technology.

I was forced to abandon the BCD-Cap technology and develop the Buck Converter in BCD.

However, the work carried out so far remains an interesting input for possible and eventual developments given the interest aroused in the process group.

## 1.4 Design Target

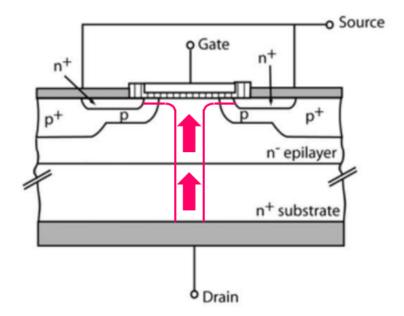

As mentioned above, BCD technology will be used for the Buck-converter design. Thanks to its versatility allows the integration of a highly efficient vertical Power DMOS ideal for the implementation of High Side Switches. This BCD technology also allows on-chip current sensing and bootstrap diode integration.

This leads to a reduction of external components, a simplification of the system with related volume and overall cost savings (Table 1.1).

| COMPONENTS          | Integrated | External |

|---------------------|------------|----------|

| DMOS                | <b>✓</b>   | -        |

| Current sense       | <b>✓</b>   | -        |

| Bootstrap Diode     | <b>✓</b>   | -        |

| Bootstrap Capacitor | -          | <b>✓</b> |

| Free Wheeling Diode | -          | <b>✓</b> |

| Inductor            | -          | <b>✓</b> |

Table 1.1: Buck Components.

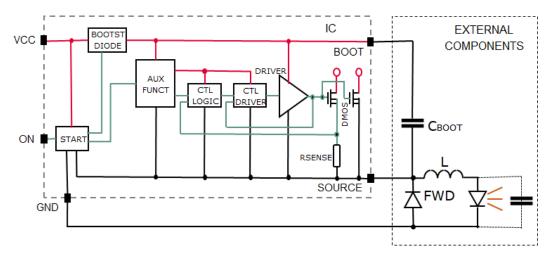

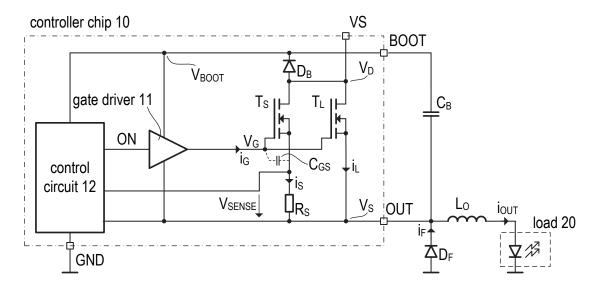

In Figure 1.7 is shown the application consisting of the IC and the external components. The functions implemented in the IC are the minimum necessary as we are currently interested in testing the high-frequency core. This explains the few PINs available. In addition to the power supply "VCC" and the ground "GND" there is the input PIN "ON" with which we switch the system ON and OFF. The output PIN

"BOOT" connects the Bootstrap capacitor while the "Source" PIN is the connection between the Power DMOS and the external circuit.

Figure 1.7: Buck Converter - IC with External Components

The three Buck converters developed all have the same architecture and only driver and  $t_{OFF}$  block have been adapted to different frequencies. In what follows, where not explicitly specified, reference will always be made to the Buck converter with the higher frequency.

## 1.5 Design Guidelines

Before starting the project, we defined the guiding specifications. This is actually an Infineon study with which we intend to verify the possibility of using the BCD technology to implement high-frequency converters, thus many functions needed in a commercial device are missing. Table 1.2 shows the guidelines we used to develop the converter.

| Parameter                           | Symbol | min | typ  | max | unit                 |

|-------------------------------------|--------|-----|------|-----|----------------------|

| Supply Voltage                      | VCC    | 7   | 13.5 | 18  | V                    |

| Operating Temperature Range         | Т      | -40 | _    | 150 | $^{\circ}\mathrm{C}$ |

| Current Consumption (not Switching) | Ignd   | _   | _    | 1   | mA                   |

| Current Consumption Standby         | Istb   | _   | _    | 500 | uA                   |

| Nominal Load Current                | Iload  | _   | 3A   | -   | A                    |

| Load Current Limitation             | Ilim   | _   | 6    | -   | A                    |

| Rds ON (25°)                        | Rds ON | _   | 80   | _   | mOhm                 |

| Rds ON (150°)                       | Rds ON | _   | 150  | _   | mOhm                 |

| Switching Frequency (Low freq)      | fsw    | _   | 1    | -   | MHz                  |

| Switching Frequency (Medium freq)   | fsw    | _   | 4    | -   | MHz                  |

| Switching Frequency (High freq)     | fsw    | _   | 10   | -   | MHz                  |

| Input Logic - High Level            | Vih    | 2   | _    | -   | V                    |

| Input Logic - Low Level             | Vil    | _   | -    | 0.8 | V                    |

| Input Logic Hysteresis              |        | -   | 0.25 | -   | V                    |

Table 1.2: Buck Converter Guidelines.

Being the high-frequency converters a topical subject, a literature research on high-frequency buck converter was carried out before starting the project. Indeed, there is a lot of material and several papers propose solutions at 10 MHz and above, all however based on Gallium nitride (GaN) technology, ([14], [15], [16]).

The GaN technology guarantees much higher switching speed than conventional silicon-based ones, and I am convinced that it will be the future for high-frequency converters. unfortunately, it is a technology currently under development that we do not have for commercial applications.

Another interesting solution is described in [17], in which a Dual Buck with a switching frequency of 25MHz based on a full differential current balance method is presented. This solution requires the measurement of the voltage at the ends of the two inductances and technology suitable for digital circuitry. It is therefore an expensive and complex system for our target and not suitable for the BCD technology we use.

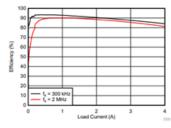

In addition to literature, a market research was carried out to see what competition offers.

In Figure 1.8 are shown some Buck converter available in the market [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] . Obviously they are not completely equivalent to what we are developing, mainly because these are commercial products that have to meet customer requirements, whereas our study is more exploratory for Infineon use. Another reason depends on the technology used, ours allows for more integration. In any case they can be considered a good comparison especially with regard to switching frequency and output current.

Figure 1.8 shows that only the best performing ones have switching frequencies of 2.0-2.5MHz, load currents of 2-2.5A and usually not simultaneously

The target we set ourselves, a switching frequency of 10MHz (in addition to the 1MHz and 4MHz Buck), the load current of 3A in the -40,150°C temperature range, is very aggressive and is considerably higher than the commercially available Buck converters. It should also be considered the  $R_{DSON}=80m\Omega$  intentionally lower than necessary in anticipation of the development of step 3 (see Figure 1.1)

| Wide Vin Step Down Devices |              |                      |                     |                      |                 |             |                               |

|----------------------------|--------------|----------------------|---------------------|----------------------|-----------------|-------------|-------------------------------|

|                            | Part No      | I <sub>out</sub> (A) | V <sub>IN</sub> (V) | V <sub>our</sub> (V) | F <sub>sw</sub> | Synchronous | Features                      |

|                            | LM34919C-Q1  | 0.6                  | 4.5 to 50           | 3.5 to 45            | 2.6 MHz         |             | Ultra-small footprint         |

| <b>□</b>                   | LM5010-Q1/Q0 | 1                    | 6 to 75             | 1.5 to 70            | 1.0 MHz         |             | Available in Q1 and Q0 grades |

| PMIC, Sync                 | TPS65310A-Q1 | 1/2                  | 4 to 40             | 0.8 to 5.5           | 0.98 MHz        | <b>V</b>    | Supports up to 5 outputs      |

| High efficiency            | LM26001/03   | 1.5/3                | 3 to 38             | 1.25 to 35           | 500 kHz, Sync   | ~           | High-efficiency sleep mode    |

|                            | LM25011-Q1   | 2                    | 6 to 42             | 2.5 to 40            | 2.0 MHz         |             | Adjustable Current Limit      |

| DCDC + LDO                 | TPS65320-Q1  | 3.2                  | 3.6 to 40           | 1.1 to 20            | 2.5 MHz         |             | LDO input auto sourcing       |

| High efficiency            | TPS54340/540 | 3.5 / 5              | 4.5 to 60           | 0.8 to 58.8          | 2.5 MHz, Sync   |             | Eco-mode                      |

| External MOS               | LM(2)5119Q   | N/A                  | 5.5 to 65           | 0.8 to 64            | 750 kHz, Sync   | ~           | Dual-channel, dual-phase      |

| External MOS               | LM(2)5117-Q1 | N/A                  | 4.5 to 65           | 0.8 to 62            | 750 kHz, Sync   | <b>V</b>    | Analog Current Monitor        |

| External MOS               | TPS40170-Q1  | N/A                  | 4.5 to 60           | 0.6 to 57            | 600 KHz         | <b>v</b>    | Pre-biased output support     |

Single products or small families (1-3 products for each application)

Figure 1.8: Buck Converters Available in the Market

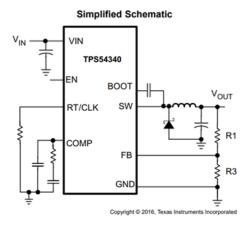

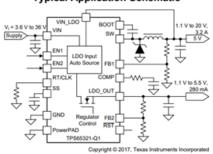

Figure 1.9 and Figure 1.10 show the first pages of the two devices datasheet that we consider to be the best performing, the TPS54340 and the TPS65320.

Even the devices mentioned are commercial buck converters, they are a good ref-

erence with regard to switching frequency and load current. In addition to frequency and output current, we also want to test the degree of integration achievable with our technology.

TPS54340

SLVSBK0D - OCTOBER 2012-REVISED MARCH 2017

#### TPS54340 42 V Input, 3.5 A, Step Down DC-DC Converter with Eco-mode™

#### 1 Features

- · 4.5 V to 42 V (45 V Abs Max) Input Range

- 3.5 A Continuous Current, 4.5 A Minimum Peak Inductor Current Limit

- Current Mode Control DC-DC Converter

- 92-mΩ High-Side MOSFET

- High Efficiency at Light Loads with Pulse Skipping Eco-mode™

- Low Dropout at Light Loads with Integrated BOOT Recharge FET

- 146 μA Operating Quiescent Current

- 1 µA Shutdown Current

- · 100 kHz to 2.5 MHz Fixed Switching Frequency

- · Synchronizes to External Clock

- Adjustable UVLO Voltage and Hysteresis

- Internal Soft-Start

- · Accurate Cycle-by-Cycle Current Limit

- Thermal, Overvoltage, and Frequency Foldback Protection

- 0.8 V 1% Internal Voltage Reference

- 8-Terminal HSOP with PowerPAD™ Package

- –40°C to 150°C T<sub>J</sub> Operating Range

- Create a Custom Design with WEBENCH Tools

#### 2 Applications

12 V, 24 V Industrial, Automotive and Communications Power Systems

#### 3 Description

The TPS54340 is a 42 V, 3.5 A, step down regulator with an integrated high side MOSFET. The device survives load dump pulses up to 45 V per ISO 7637. Current mode control provides simple external compensation and flexible component selection. A low ripple pulse skip mode reduces the no load supply current to 146  $\mu A$ . Shutdown supply current is reduced to 1  $\mu A$  when the enable pin is pulled low.

Undervoltage lockout is internally set at 4.3 V but can be increased using the enable pin. The output voltage start up ramp is internally controlled to provide a controlled start up and eliminate overshoot.

A wide switching frequency range allows either efficiency or external component size to be optimized. Frequency foldback and thermal shutdown protects internal and external components during an overload condition

The TPS54340 is available in an 8-terminal thermally enhanced HSOP PowerPAD $^{\rm TM}$  package.

#### Device Information

| ORDER NUMBER | PACKAGE  | BODY SIZE        |

|--------------|----------|------------------|

| TPS54340DDA  | HSOP (8) | 4.89 mm x 3.9 mm |

Figure 1.9: TPS54340 Datasheet

TPS65320D-Q1

# SLVSE56 -NOVEMBER 2017 TPS65320D-Q1 36-V Step-Down Converter With Eco-mode™ and LDO Regulator

#### 1 Features

- · Qualified for Automotive Applications

- AEC-Q100 Qualified with the Following Results:

- Device Temperature Grade 1: -40°C to +125°C Ambient Operating Temperature

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C4B

- One High-VIN Step-Down DC-DC Converter

- Input Range of 3.6 V to 36 V

- 250-mΩ High-Side MOSFET

- Maximum Load Current 3.2 A, Output Adjustable 1.1 V to 20 V

- Adjustable Switching Frequency 100 kHz to 2.5 MHz

- Synchronizes to External Clock

- High Efficiency at Light Loads With Pulse-Skipping Eco-mode™ Control Scheme

- Maximum 140-μA Operating Quiescent Current

- · One Low-Dropout Voltage (LDO) Regulator

- Input Range of 3 V to 20 V, With Auto-Source to Balance Efficiency and Lower Standby Current

- 280-mA Current Capability With Typical 35-µA Quiescent Current in No-Load Condition

- Power-Good Output (Push-Pull)

- Low-Dropout Voltage of 300 mV at I<sub>O</sub> = 200 mA (Typical)

- · Overcurrent Protection for Both Regulators

- · Overtemperature Protection

- 14-Pin HTSSOP Package With PowerPAD™ Integrated Circuit Package

#### 2 Applications

- Automotive Infotainment and Cluster

- · Advanced Driver Assistance System (ADAS)

- Automotive Telematics, eCall

#### 3 Description

The TPS65320D-Q1 device is a combination of a high-VIN DC-DC step-down converter, referred to as the buck regulator, with an adjustable switch-mode frequency from 100-kHz to 2.5-MHz, and a high-VIN 280-mA low-dropout (LDO) regulator. The input range is 3.6 V to 36 V for the buck regulator, and 3 V to 36 V for the LDO regulator. The buck regulator has an integrated high-side MOSFET. The LDO regulator features a low-input supply current of 45- $\mu$ A typical in no-load, also has an integrated MOSFET with an active-low, push-pull reset output pin. The input supply of the LDO regulator auto-source from the output of the buck regulator when it is in operation. Low-voltage tracking feature enables TPS65320D-Q1 to track the input supply during cold-crank conditions.

The buck regulator provides a flexible design to fit system needs. The external loop compensation circuit allows for optimization of the converter response for the appropriate operating conditions. A low-ripple pulse-skip mode reduces the no-load input-supply current to maximum 140  $\mu\text{A}.$

The device has built-in protection features such as soft start, current-limit, thermal sensing and shutdown due to excessive power dissipation. Furthermore, the device has an internal undervoltage-lockout (UVLO) function that turns off the device when the supply voltage is too low.

#### Device Information<sup>(1)</sup>

| PART NUMBER  | PACKAGE     | BODY SIZE (NOM)   |

|--------------|-------------|-------------------|

| TPS65320D-Q1 | HTSSOP (14) | 5.00 mm × 4.40 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

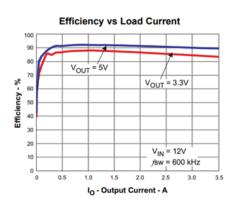

#### **Buck Efficiency Versus Output Current**

Figure 1.10: TPS65320 Datasheet

#### Typical Application Schematic

# 1.6 Integrated Development

In summary, the second step of our program consists of three Buck converters design and their layouts. The layouts will be placed on a shared test chip for prototyping. Prototypes will be measured in the laboratory by building appropriate test PCBs optimised to work at different switching frequencies. The number of PCB layers will

be minimised, and the definition of test-point positioning for prototype measurement will be optimised by simulations with appropriate development software.

The all development steps are shown in Figure 1.11.

Figure 1.11: Process Flow Overview

# Chapter 2

# **Buck Converter Architecture**

## 2.1 Floating Control Logic

In Buck Converters the Power DMOS having Drain connected to  $V_{CC}$  and Source to the inductor floating side, floats between GND and  $V_{CC}$ . So must do the Driver that drives it, being fed between the Bootstrap capacitance and Source.

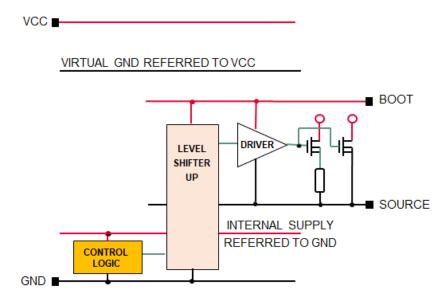

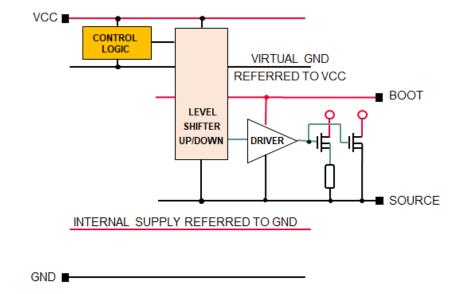

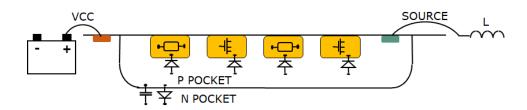

Therefore, one of the first topics addressed was the definition of the power lines architecture to be adopted in the IC. The often-used solution of low-side control and auxiliary circuits (Figure 2.1) has the simplicity of requiring supply lines referred to GND. Conversely, this architecture requires level shifters [28] [29] to transfer commands, feedback and protection signals from the circuits referred to GND to the circuits located between the Bootstrap and Source lines and vice versa. Level shifters take time to transfer signals and cause delays. Moreover parasitic capacitive couplings between the substrate 'n' connected to VCC and the 'p' pockets of the floating electrical components are cause of parasitic capacitive currents that dirty the transferred signals when they do not even overwrite them, causing the device to malfunction.

The other solution shown in Figure 2.2 requires for control and auxiliary circuits a power supply between VCC and a virtual ground few volts below VCC (very often 3V), but requires level shifters capable of transferring signals in two directions, to GND and to the power supply provided by the Bootstrap capacitance. This makes the situation described above even worse.

It was therefore decided for a different solution, preferring to have all the circuits controlling the Power DMOS floating (Figure 2.4) and fed between Bootstap and Source. This solution does not require level shifters, as all the monitoring and control signals access the switching parts directly, which speeds up the whole system.

In order to eliminate the effects of the capacitive currents to the substrate generated by the switching, all floating circuits are placed in a doped 'p' pocket (Figure 2.3), and polarised at the low-impedance Source node, which collects the parasitic capacitive currents and neutralises their effects. The circuits, fed between Bootstrap and Source are in parallel to the  $C_{BOOT}$  capacitor. This is comparable to a voltage supply and constitutes a short circuit for disturbances.

Figure 2.1: Control Logic GND Referred Plus UP Level Shifter

Figure 2.2: Control Logic VCC Referred Plus UP/DOWN Level Shifter

Figure 2.3: "p" Pocket Shield

Figure 2.4: Floating Control Logic

## 2.2 Block Diagram

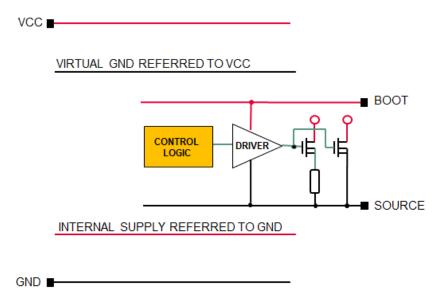

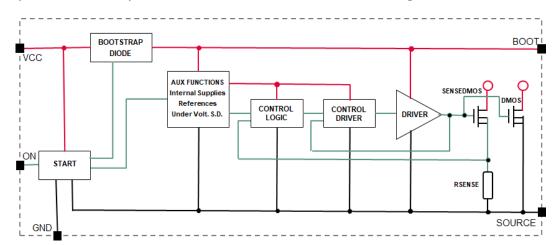

Having defined the power supplies, consider now the block diagram of the Buck Converter (Figure 2.5).

The battery via the VCC pin directly supplies the 'Start' block and the 'Bootstrap Diode' block.

The 'Start' block is the only one referred to GND and is interfaced with the outside via the 'ON' pin. Only if "ON" is high the converter is active. The "Start" block recognises the status of the "ON" pin and sends the power signal to the "Bootstrap Diode" block and the "Aux Functions" block.

"Bootstrap Diode" is responsible for charging the external capacitance  $C_{BOOT}$  to the desired voltage.  $C_{BOOT}$  is charged by the diode when the "Source" pin is close to GND, however, when "Source" rises towards VCC the diode is OFF because reverse polarised.

The 'Aux Functions' block is activated as soon as  $C_{BOOT}$  is loaded to the correct value. It consists of several sub-blocks, the main ones being "Internal Supplies" which generates the supply for the entire floating part, "References" which, thanks to the Band-gap, generates the voltage and current references, the "Under Voltage Shut-Down" which activates the entire floating part when the supplies, voltage and current references reach the required values.

The 'Control Logic' and 'Control Driver' blocks control system and driver for the correct operation of the buck converter.

The 'Driver' block switches the Power DMOS ON and OFF according to the signal provided by the previous blocks. In conventional solutions, the Driver is powered at the same voltage that has to be transferred to the Power DMOS Gate (often 3V). In this project, anticipating the Driver section, we power it at 6-7V in order to charge the Power DMOS gate to 3V faster. This requires a proper control, which explains the presence of the "Control Driver" block.

Finally, the Power DMOS with its current sense formed by a fraction of the Power-DMOS with the  $R_{SENSE}$  resistor in series. The voltage drop across  $R_{SENSE}$

(a few tens of mV) constitutes the feedback of the Control Logic circuit.

Figure 2.5: Buck Converter IC Block Diagram

## 2.3 Fixed $t_{OFF}$

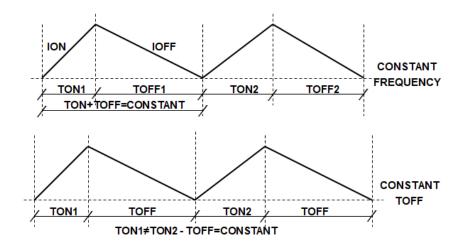

Another point to be defined is the frequency control

Fixed frequency control [30] [31], [32] is the solution often used, the period  $T = t_{ON} + t_{OFF}$  is constant. If a perturbation causes a variation  $\Delta t_{ON}$  the control will cause a variation  $\Delta t_{OFF} = -\Delta t_{ON}$  so that the period remains constant. Normally in fixed-frequency controls,  $R_{SENSE}$  monitors the load current throughout the cycle. It is usually external and the voltage across it is the feedback signal. It is brought to the on-chip control circuit via a PAD.

A fixed-frequency DC-DC converter oscillates when the duty-cycle ( $d = t_{ON}/T$ ) is less than 0.5. The Slope Compensation technique is used to eliminate the oscillations [30] [31], [33].

Other methods of controlling switching frequency are Fixed  $t_{ON}$  [34], [35], [35] and Fixed  $t_{OFF}$  [36], [37], [38], [39], [40].

Fixed  $t_{ON}$  and Fixed  $t_{OFF}$  are one the dual of the other. Preferring one or the other depends on the type of application.

In our case, as the current sensing is on-chip and the internal  $R_{SENSE}$  is necessarily placed in series with the Power DMOS, we can only measure the current during  $t_{ON}$  as during  $t_{OFF}$  the load current recirculates externally through the freewheeling diode and the control system is blind.

The choice of Fixed  $t_{OFF}$  control was forced. In addition, this choice minimise the PINs, reduce the external components and simplify the PCB.

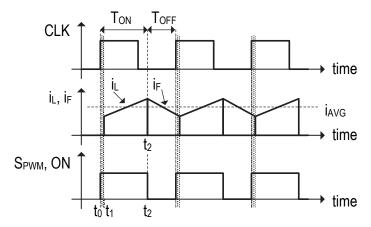

(Figure 2.6) shows the difference between constant frequency and Fixed  $t_{OFF}$ . In case of constant frequency the control system reacts to load variations and disturbances by varying the duty-cycle, while in case of fixed  $t_{OFF}$  by varying  $t_{ON}$ .

In the cases of Fixed  $t_{OFF}$  and Fixed  $t_{ON}$  controls, one speaks of quasi constant frequency.

2.3 Fixed  $t_{OFF}$

Figure 2.6: Fixed Frequency Versus Fixed  $t_{OFF}$

# Chapter 3

# Start and Bootstrap Diode Blocks

#### 3.1 Start Block

The Start and Bootstrap Diode blocks are the only ones connected to VCC.

The principle diagram of the Start block is shown in Figure 3.1. The ON pin is connected after the ESD protections to the HV (high voltage) switch  $M_1$  which enables the current generator  $I_1$ . The current  $I_1$  constitutes the drive signal for the bootstrap diode. Simultaneously with a similar circuit  $(M_2, I_2)$  the Feed Forward (FF) function is activated [41].

The Feed Forward function generates a signal proportional to the supply voltage VCC and changes the  $t_{ON}$  in presence of changes in VCC, so the work of the control loop is lightened accordingly and the stability of the output variable is increased, indeed recall that  $V_{out} = V_{in}(t_{ON}/T) = V_{in} D$ . The Start block is fed by PIN 'ON', while the connection to VCC is the feedback for the Feed Forward function.

When the PIN ON returns to GND, the information is purposely transferred with a certain delay (R,C) to the HV switch M3, which similarly to the previous cases, via I3, generates the shutdown signal for the entire system. The R-C delay is necessary both to avoid uncertainties during transitions and to give the control the necessary time to properly set the system for shutdown.

It should be noted that these are the only level-shifters in the Buck Converter and that the transmitted signals are in DC current as they are more immune to transitions between GND and VCC than voltage signals.

Figure 3.1: Start Block

## 3.2 Bootstrap Diode Block

When the Power DMOS is ON, its resistance is close to zero and brings the Source to a voltage value close to VCC. In this condition, all floating circuits are powered by the bootstrap capacitance loaded to a predefined value in the previous half-cycle. The bootstrap capacitance being of high value (from a few nF up to  $\mu$ F) constitutes for practical purposes a voltage supply.

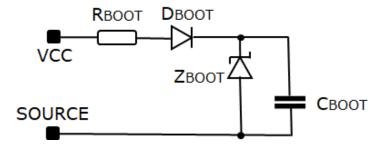

In the discrete component solution, the implementation of the bootstrap capacitance charging circuit is quite simple (Figure 3.2). When the DMOS is OFF, the Source line is close to GND and the directly biased diode allows charging of the  $C_{BOOT}$  capacitance. The zener diode  $Z_{BOOT}$  defines the voltage of  $C_{BOOT}$  while the resistor  $R_{BOOT}$  limits the current drawn by VCC. When the DMOS is ON, the Source line is close to VCC and the inversely biased diode prevents the discharge of the  $C_{BOOT}$  capacitor.

This solution has some drawbacks, because more components are needed and more area is requested in the PCB, all of these translates into higher costs. Another drawback is the power consumption through  $Z_{BOOT}$  and  $R_{BOOT}$ , the latter of which must limit the current to rather high values in order to allow the system to function.

Figure 3.2: Bootstrap Diode, Discrete implementation

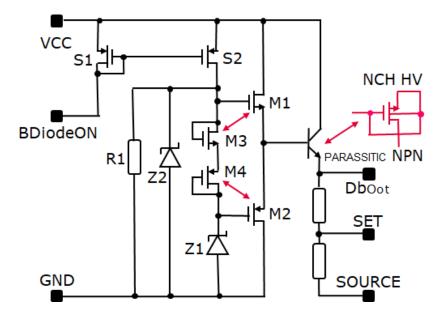

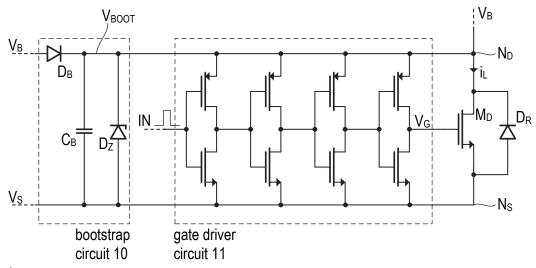

The Bootstrap diode on chip realisation is necessarily different as no zener capable of carrying high currents is available and only reduced power dissipation is allowed. In Figure 3.3 is shown an outline schematic of the on chip Bootstrap Diode implementation [42].

Figure 3.3: Bootstrap - Principle Schematic

The Diode-ON current signal activates via the current mirror  $S_1$ - $S_2$  the Bootstrap Diode bias circuit, this stage resembles the output of class AB amplifiers.

The output of the complementary pair  $M_1$ - $M_2$  feeds the npn-HV bipolar capable of delivering over a hundred mA to quickly charge the bootstrap capacitance.  $M_3$  and  $M_4$  coupled with  $M_1$  and  $M_2$  plus  $Z_2$  setting the base voltage of the npn, define the voltage of  $C_{BOOT}$  to approximately 7V. The zener  $Z_1$  is a maximum voltage protection. The central point SET, of the resistive divider  $R_2$ - $R_3$ , is the signal that enables the Buck Converter to function. When the bootstrap capacitance reaches 7V the bipolar  $Q_1$  and the MOS  $M_1$  are interdicted and the current drawn is reduced to that of the mirror  $S_1$ - $S_2$ .

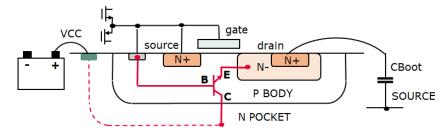

Unfortunately, the bipolar npn-HV component is not available in the technology. The nch HV parasitic npn was therefore used (Figure 3.4)

Figure 3.4: npn - Parassitic in High Voltage nch

The MOS nch HV having the gate, source and body short circuited is disabled. In Figure 3.4 the npn is shown in red, the substrate woks as collector, the pbody as base and the drain as emitter. The drain-emitter having the drain-extension has a breakdown voltage higher than the junction  $N^+ PBody$  and is not damaged when the Power DMOS is ON and the voltage of the bootstrap capacity is about 7V above VCC.

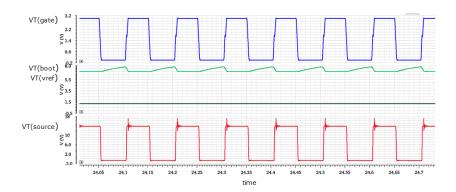

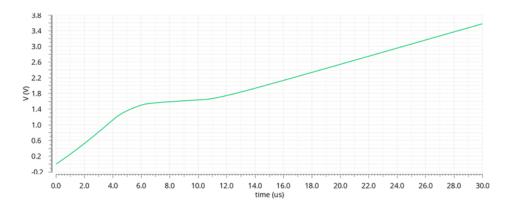

Figure 3.5 shows the simulated behaviour of the bootstrap diode and the voltage across the bootstrap capacitance. It can be seen that during  $T_{OFF}$  as the diode is in

conduction the capacitance is charged, and during the  $T_{ON}$  pulse when the DMOS gate is charging shows a rapid drop in voltage. When 3V is reached at the gate, the charge transfer ceases and the voltage on the capacitance remains constant until the next  $T_{OFF}$ .

Figure 3.5: Bootstrap Diode behaviour

# Chapter 4

# **Auxiliary Blocks**

#### 4.1 Introduction

In this chapter we describe the auxiliary circuits. The task of these circuits is to define the boundary conditions necessary for the proper functioning of the buck converter's control blocks.

The auxiliary blocks are 'Supply', 'Bandgap' and 'UVSD' (Under Voltage Shut Down), all of which are floating circuits, i.e. fed between Bootstrap capacitor and Source.

## 4.2 Supply Block

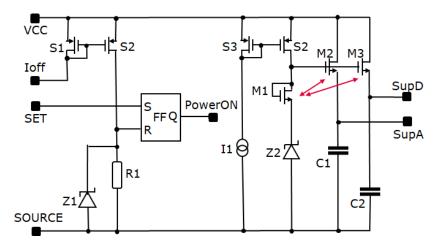

The 'Supply' block essentially performs two tasks, the first is to supply the voltages to the floating circuits, the second, once the supplies are present, is to give the 'Power ON' signal to the subsequent blocks. The schematic diagram is shown in Figure 4.1. "Supply" is necessarily powered by the Bootstrap capacitor (approx. 7V) as this is currently the only power supply available.

As soon as the block is energised, the two supplies, analogue (supA) and digital (supD), are generated independently. The supA power supply is dedicated to circuits that require current continuously, while supD supplies digital blocks that typically require pulsed currents. This reduces interference between the analogue and digital parts.

A set-reset flip-flop generates the "Power ON" signal. It is set by the "Set" signal generated in the "Bootstrap Diode" block. The "OFF" current signal from the "Start" block is converted into a voltage signal via resistor  $R_1$ , which resets the flip-flop and consequently switches off the Buck Converter. The voltages  $S_{UPA}$  and  $S_{UPD}$  are defined by a circuit represented for simplicity by zener  $Z_2$ . Being  $M_1$ ,  $M_2$  and  $M_3$  matched they have the same  $V_{GS}$ , it follows that  $S_{UPA} = V_{Z2} + V_{GSM1} - V_{GSM2}$  and similarly for  $S_{UPD}$ .

Figure 4.1: Supply - Principle Schematic

## 4.3 Bandgap Block

Voltage references are essential circuits in any electronic circuit, whether discrete or integrated. A reference circuit must be well-defined and insensitive to changes in temperature, power supply and load. In the past, the zener diode was often used as a voltage reference [42]. The zener breakdown voltage essentially involves two physical phenomena, ranging from the tunnel effect for low zener voltages with a negative temperature coefficient to the avalanche effect at high zener voltages with a positive temperature coefficient. In the intermediate range, the two phenomena coexist, and as the zener voltage increases, there is a gradual change from a negative to a positive temperature coefficient. The balance between the two generating a coefficient close to zero corresponds to a zener voltage of about 5V.

In integrated circuits, they are no longer used as a reference for several years, either because the zener values obtained is too high in relation to the circuit requirements or because they did not guarantee the required accuracy. Bandgap (BGR) circuits are universally used for voltage references [42]. Bandgap is usually used as a constant voltage reference. From the Bandgap, the reference voltages for the entire chip are generated.

Frequently, in the bandgap circuit starting from the reference voltage, a current references is also derived, but as  $I_{REF} = V_{BANDGAP}/R$  the production spread and the thermal coefficient of R affect  $I_{REF}$ , which must at least be compensated in temperature. Trimming is used to correct the value. Unfortunately, the current bandgap does not exist.

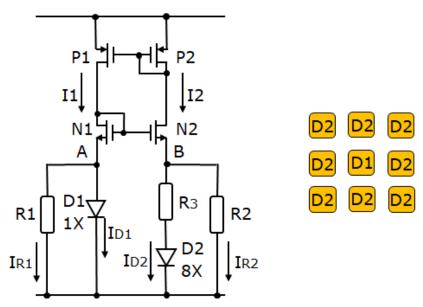

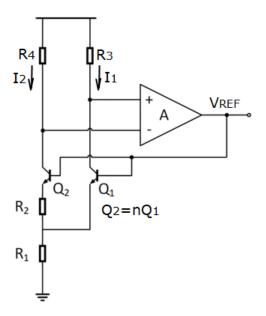

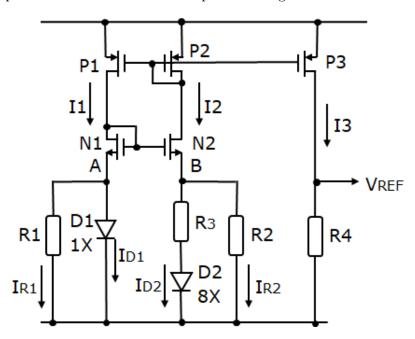

The Bandgap core of implemented circuit is shown in Figure 4.2

The diodes  $D_1$  and  $D_2$ , where  $D_2 = nD_1$  play a fundamental role in the bandgap, values normally used for n are 8 or 10. In our case n=8 because this value allows the centroid layout, where the diode of multiplicity 1 stands in the centre.

Being the voltage on the diode

$$V_D = V_T \ln(I_D/I_S)$$

where  $V_T = KT/q$  (4.1)

results

$$V_{D1} - V_{D2} = \Delta V_D = V_T \ln(I_{D1}/I_{S1} * I_{S2}/I_{D2})$$

(4.2)

since

$$I_{D1} = I_{D2}$$

and  $I_{S2} = nI_{S1}$  (4.3)

results

$$\Delta V_D = V_T \ln(n)$$

for n=8 a 25°C  $\Delta V_D = 52mV$  (4.4)

There are also circuit symmetries:  $P_1 = P_2$  and  $N_1 = N_2$  form two current mirrors with a 1:1 ratio,  $R_1 = R_2$ , and as already mentioned  $D_2 = 8D_1$ .

The currents  $I_1$  and  $I_2$  are forced to be equal by the mirrors, also the voltages at the sources of  $N_1$  and  $N_2$  must be equal and equal to the voltage across  $D_1$ . It follows that  $I_{R1} = I_{R2}$ . From this we obtain the relation

$$I_{R1} = I_{R2} = V_{D1}/R_1 \tag{4.5}$$

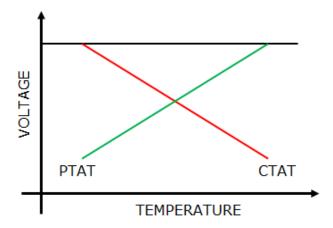

$V_{D1}$  has a thermal coefficient (NEGATIVE) of -2mV/°C - known as CTAT (Complementary To Absolute Temperature)

The voltage drop at the ends of  $R_2$  is  $V_{D1}$ - $V_{D2} = \Delta_{VBE}$ . Hence the second relationship:

$$I_{D2} = \Delta V_{BE}/R_3 \tag{4.6}$$

$DV_{BE}$  has a (POSITIVE) thermal coefficient proportional to KT, known as PTAT (Proportional To Absolute Temperature). Since

$$I_1 = I_2 = I_{R1} + I_{D1} = I_{R2} + I_{D2}$$

must be  $I_{D1} = I_{D2}$  (4.7)

$I_1$  and  $I_2$  are the contribution of two terms proportional to CTAT and PTAT.

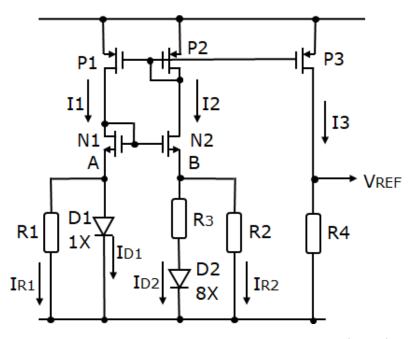

Now simply mix the curents  $I_{R1} = I_{R2}$  and  $I_{D1} = I_{D2}$  in the right proportion and complete the bandgap circuit as in Figure 4.3 into which mirror  $P_3$  (mirror ratio 1:1) and resistor  $R_4$  have been added. The resistors  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_4$  are coupled and the same type to have equal thermal coefficient.

Figure 4.2: Implemented Bandgap Core

Since  $I_1 = I_2 = I_3$  and since diodes in integrated circuits are always bipolars with base and emitter short-circuited, we shall henceforth denote  $V_D$  by  $(V_{BE})$ . We can therefore write

$$(V_{BE}/R_1 + \Delta V_{BE}/R_3) * R_4 = V_{ref} \tag{4.8}$$

If we set  $R_3 = KR_1$  we obtain

$$(V_{BE}/R_1 + \Delta V_{BE}/KR_1) * R_4 = V_{ref}$$

(4.9)

which becomes

$$(V_{BE} + \Delta V_{BE}/K) * R_4/R_1 = V_{ref}$$

(4.10)

K is not only the ratio between the resistances  $R_3$  and  $R_1$  but also the mixing factor of the terms CTAT and PTAT. By choosing it appropriately we can give to our voltage reference the slope we desire, not necessarily zero.

A curiosity, by properly choosing k, the currents  $I_{D2}$  and  $I_{R2}$  can be mixed so that the current  $I_2$  is constant in temperature. However, it must be taken into account that is possible to pass from voltage to current only via a resistor which usually is affected by the production spread. The current reference will have the same spread despite having zero thermal coefficient.

Figure 4.3: Bandgap core with reference voltage  $(V_{REF})$

Figure 4.4 shows the contributions of the PTAT and CTAT currents. When poperly mixed the reference voltage is constant.

Figure 4.4: PTAT Vs CTAT

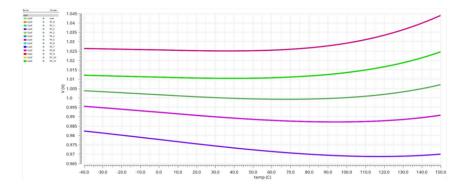

Figure 4.5 shows the PV (Process-Voltage) simulation over temperature of the implemented bandgap. The reference value is 1V and the simulated temperature range is  $(-40^{\circ}\text{C}-150^{\circ}\text{C})$ , typical automotive.

Figure 4.5: Voltage Reference - PV Simulation

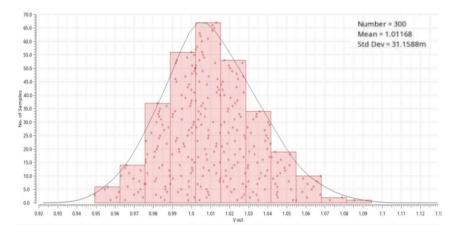

The Monte Carlo simulation is shown in Figure 4.6. The mean value is 1.01V and sigma is 0.03%.

Figure 4.6: Bandgap - Montecarlo simulation

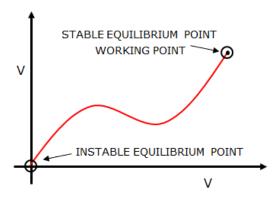

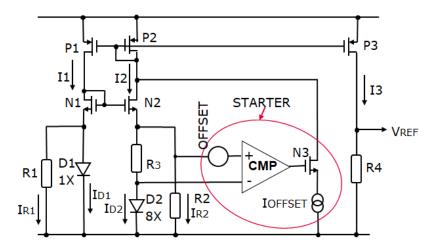

There is one last point to discuss, the 'Starter'. Bandgaps have multiple equilibrium points besides the working point and the Starter is the circuit that avoids unwanted equilibrium points and moves the Bandgap to the desired working point.

The Brokaw cell has two equilibrium points [42], one in the origin, which is unstable, and a second stable one which is the working point. Simply diverting the Brokaw cell from the equilibrium point at the origin is enough to make it evolve towards the stable equilibrium point.

Unfortunately, the Brokaw circuit requires too high supply voltage for many current requirements. Therefore, different circuit topologies are used, which are developed in "parallel" rather than "series" to reduce the supply voltage. We also use one of these in the Buck Converter.

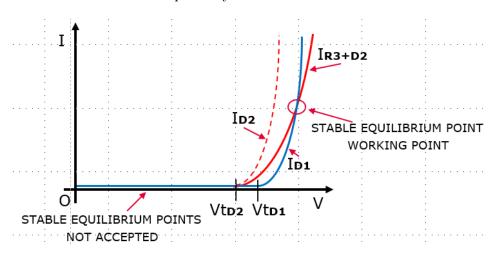

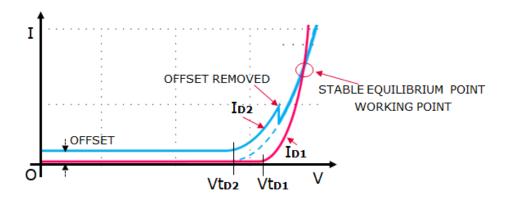

Unfortunately, these have infinities plus 1 stable equilibrium points. In Figure 4.7 it can be observed from the I-V characteristics of the diode  $D_1$  and the series  $R_3 + D_2$  that  $Vt_{D2} < Vt_{D1}$  and the current  $I_{R3+D2}$  due to the series resistance  $R_3$  grows more slowly than the current  $I_{D1}$ . The two curves cross at the stable equilibrium point that we want as working point.

All other points in the segment  $O-Vt_{D2}$  are undesirable equilibrium points. In fact, in that segment, the currents  $I_{D2}=I_{D1}$  are zero and  $I_{R1}=I_{R2}$  even if different from 0 fulfil the conditions imposed by the circuit.

Figure 4.7: Bandgap Stable Equilibrium Points

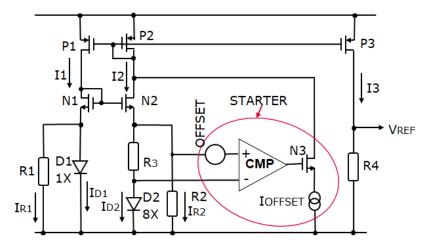

We therefore need an appropriate 'Starter' that forces the bandgap to the desired working point. The one used in this Buck Converter is shown in Figure 4.8. The starter consists of a comparator with an intrinsic offset and inputs connected to the ends of  $R_3$ . Connected at the comparator output there are a switch  $N_3$  with the current generator  $I_{OFFSET}$  in series.

In the segment  $O-Vt_{D2}$  the comparator inputs have the same null voltage, but due to the intrinsic offset (approx.  $25_{mV}$ ,  $30_{mV}$ ) the output of the comparator being high, enables the switch  $N_3$  and the generator  $I_{OFFSET}$  starting a regenerative loop which ends only when a voltage equal to the intrinsic offset appears at the comparator inputs. At this point the offset is removed and the bandgap evolves to the working point.

Figure 4.8: Bandgap Circuit Plus Starter Circuit

### 4.4 UVSD - (Under Voltage Shut Down) Block

The start-up moment of an integrated circuit is one of the most critical phases because at start-up, digital circuits, but also analogue ones, can assume states that do not guarantee a regular evolution of the device.

The UVSD is the block that gives the OK for the device to do what it was designed to do. This does not mean that before the OK the circuits are asleep. Quite the contrary, they are working on getting the circuits set up properly to allow a regular start. Let's take a digital and an analogue example. For a flip-flop, it is not equivalent to start with set or reset, the evolution can be completely different. Or for an OPA within a loop, starting with the compensation capacity unloaded or loaded to maximum voltage can make the difference between good operation or load failure.

The UVSD OK is not only dependent on the supply voltage of the various blocks, but also on the feedback from other blocks, e.g. the bgap-OK signal provided by Bandgap.

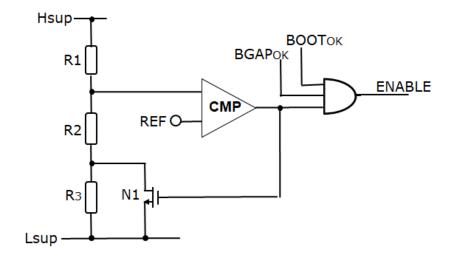

In the Buck converter design, in addition to monitoring the internal supply voltages, the UVSD is conditioned by feedback from bandgap and bootstrap voltage (Figure 4.9).

$R_3$  is in series with  $R_1$  and  $R_2$  or short-circuited depending on the output of the comparator CMP. When the relation

$$(H_{SUP} - L_{SUP}) \left( \frac{R_2 + R_3}{R_1 + R_2 + R_3} \right) \ge V_{REF}$$

(4.11)

together  $BGAP_{OK}$  and  $BOOT_{OK}$  the Buck converter is enabled. When

$$(H_{SUP} - L_{SUP}) \left(\frac{R_2}{R_1 + R_2}\right) < V_{REF}$$

(4.12)

the Buck Conveter is disabled

Figure 4.9: UVSD - Under Voltage Shut Down

# Chapter 5

# Control Driver

#### 5.1 Introduction

In DC-DC converters the transfer of energy between input and output occurs with an intermediate storage of energy packets in the reactive components L and C. The storage is cyclic and is imposed by the switching frequency of the DMOS. It follows that the higher the frequency, the lower the energy stored in the single period in the L and C components. Therefore smaller reactive components, lower cost and lower volume required.

The driver plays a key role, as faster driver allows higher switching frequency with the advantages mentioned above.

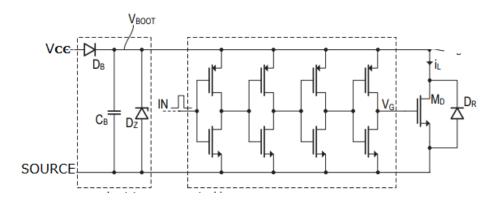

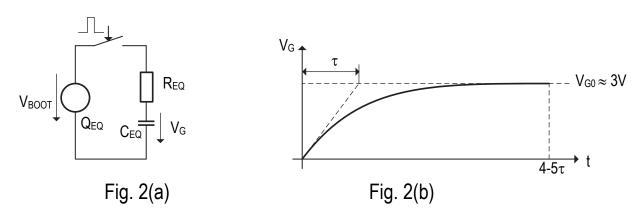

A typical implementation is shown in Figure 5.1. Since the DMOS in ON condition has the source close to  $V_{CC}$ , the gate must be driven at a higher voltage. This voltage, provided by the bootstrap capacitor, is applied to the gate of the DMOS via the driver. Typically the driver is a series of trumpets as shown in figure.

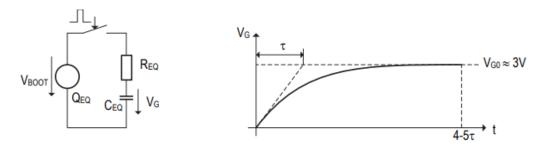

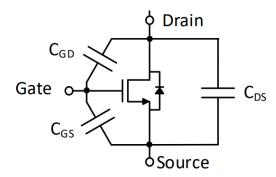

If we call with Req the output resistance of the driver and approximate the input capacity of the DMOS with Ceq, we obtain the circuit in Figure 5.2. The time requested to charge Ceq is about 5 time constants,  $5\tau = 5R_{eq}C_{eq}$ .

It must be said that assimilating the charge of DMOS to the charge of capacity is a simplification. As explained in the Appendix, the capacitance between gate and drain  $C_{GD}$  plays a fundamental role in the charge of the DMOS

Figure 5.1: Example of Typical Driver Implementation

30 Control Driver

Figure 5.2: Driver Equivalent Circuit and Charging Capacitor Timing

### 5.2 High Speed Driver

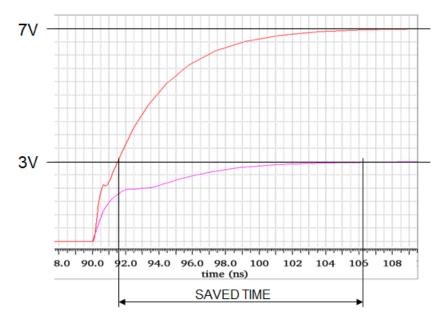

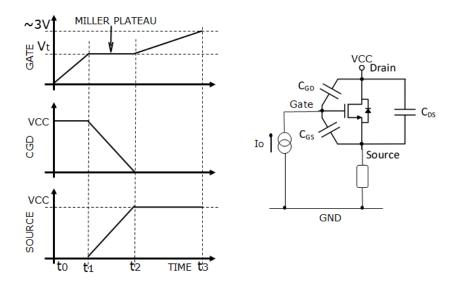

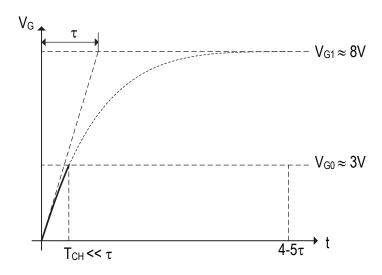

An idea to increase the speed of the driver is to load the voltage of the Bootstrap capacitor with a higher voltage, in this way the Ceq capacity reaches the required voltage more quickly. The simulation of the DMOS gate charged with Bootstrap capacity loaded at 3V and 7V is shown in Figure 5.3, the time savings to charge the gate to 3V is dramatic .

Figure 5.3: Difference in Charging DMOS with Bootstrap Voltage 3V and 7V

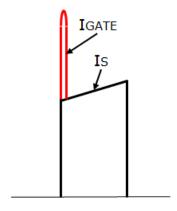

Observing the simulation it is also obvious that is required to stop immediately as soon as the gate reaches the allowed voltage otherwise the DMOS is destroyed. The solution of measuring the instant in which the gate reaches right voltage with a comparator can be accepted only for very low switching frequencies, i.e. only when the gate charge time is much greater than the comparator delay Figure 5.4.

Figure 5.4: Gate Voltage Sensed with a Comparator

For high switching frequency a different approach is needed.

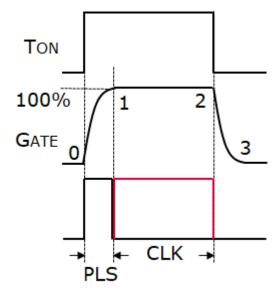

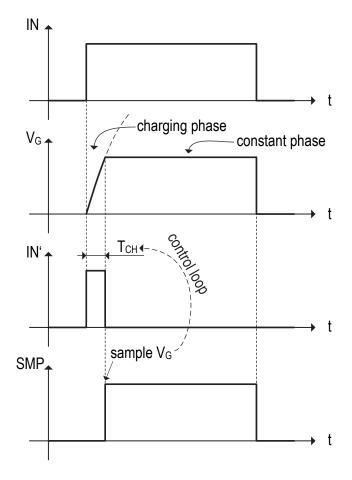

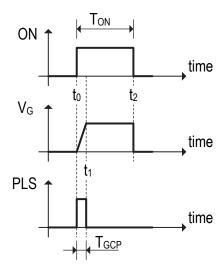

We can start by considering the Ton signal coming from the control circuit and the gate of the DMOS Figure 5.5, for convenience of explanation we divide the gate voltage into three parts, "turn ON" (1-2), "DMOS ON" (2-3) and "turn OFF" (3-4).

The turn ON is the real charging phase, the current supplied by  $C_{BOOT}$  through the driver charge the gate of the DMOS. In the next phase the DMOS is ON and is not loaded further.

Suppose to measure the turn-ON time (0-1) and from this generate the "PLS" pulse. The time interval between 1 and 2 define the "CLK" pulse. The sum of PLS and CLK is equal to  $T_{ON}$ . The interval (2-3) is the turn-OFF time.

Figure 5.5: Relation Between Ton, PLS and CLK

Now let's do the opposite procedure. At the beginning of  $T_{ON}$  the PLS pulse is generated and with this the driver is activated, the driver is ON only during PLS, and during the rest of  $T_{ON}$ , that is CLK, it is OFF. We are thus sure that at the end of PLS the gate of the DMOS has reached the right value.

Now a method must be found to generate the PLS and CLK pulses.

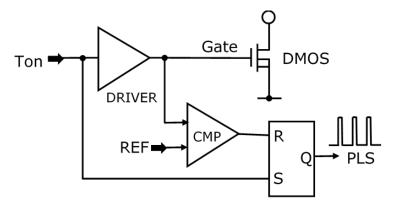

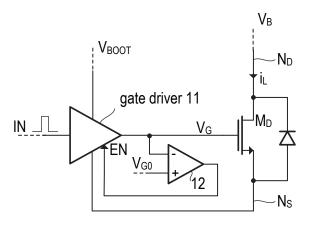

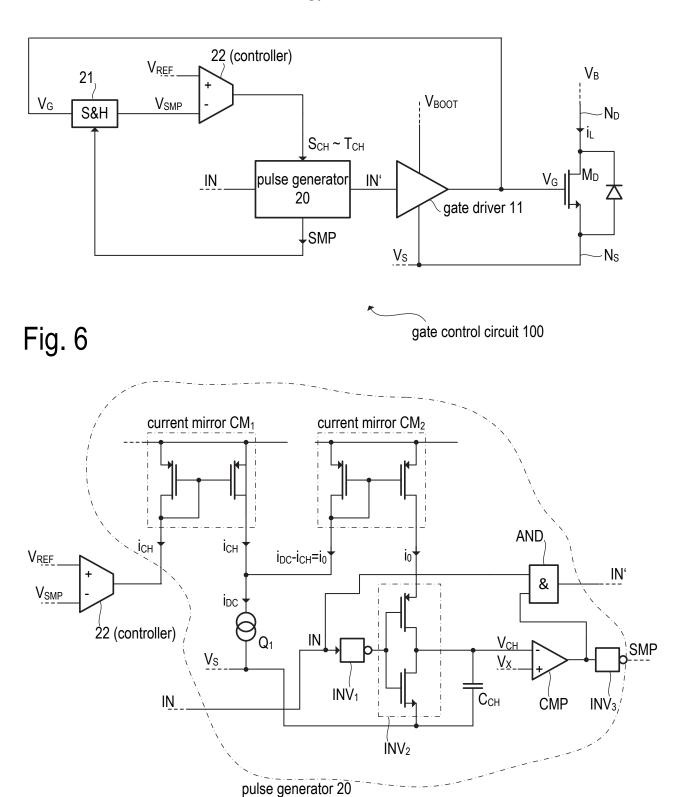

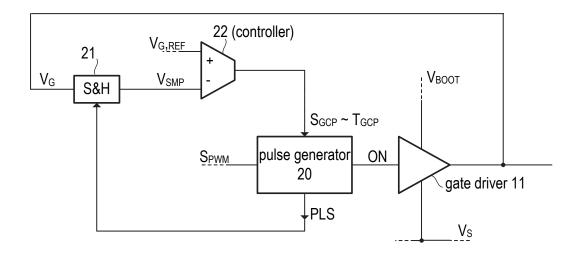

The block circuit that implements the above mentioned control is shown in Fig-

32 Control Driver

ure 5.6. The pulse generator activated by  $T_{ON}$  sends the PLS pulse to the driver which loads the DMOS gate. Once PLS is finished, the CLK pulse begins and, by switching ON the synchronous switch, allows the  $C_{STORE}$  capacitor to store the gate voltage. The OPA compare the voltage across  $C_{STORE}$  with the voltage reference. The  $OPA_{OUT}$  output acts on the pulse generator to modulate PLS.

In other words, a feedback control, reading the gate voltage defines the driver switch-on time.

Figure 5.6: Circuit Loop that Generate PLS and CLK Pulses

Much attention must be paid at the start to avoid too long pulses. A Soft Start is therefore recommended. As soon as the DC-DC is turned on, a PLS pulse of minimum width is defined and not sufficient to reach the correct gate voltage, thus the closed loop control widens the pulse until the desired gate voltage is reached.

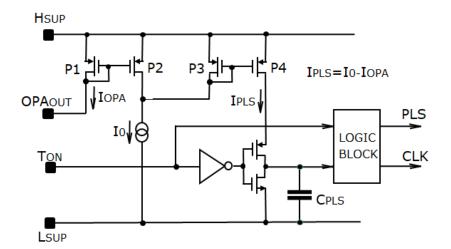

Figure 5.7 shows the block diagram of the circuit that generates the PLS and CLK pulses. Current  $I_{PLS}$  is the difference between the DC current  $I_0$  and the current  $I_{OPA}$  delivered by the OPA. At the beginning of  $T_{ON}$  starts to loads the capacitance  $C_{PLS}$ . The "logic block" senses the capacitor voltage and depending on it defines the PLS and CLK pulses width. The current  $I_{PLS}$ , modulated by the OPA, charges  $C_{PLS}$  more or less quickly, thus defining PLS.

Figure 5.7: Pulse Generator Block

#### 5.3 Driver Control Simulations

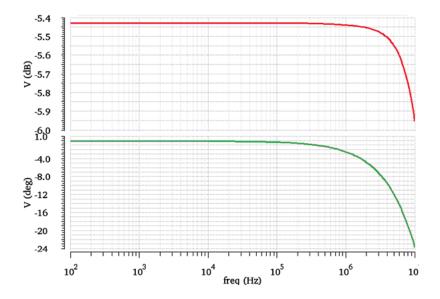

This paragraph shows some simulations of the Contol Driver related to the 10MHz Buck Converter.

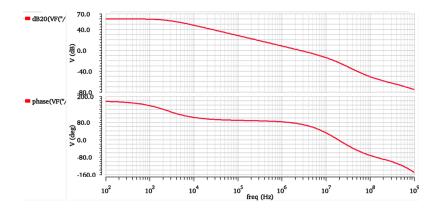

In Figure 5.8 is shown the control driver loop stability. The Bode diagram reaches 0dB with 20dB/dec and shows a phase margin of about 75°.

Figure 5.8: Control Driver Loop Stability

The Figure 5.9 shows for OPA a Gm at input balance of 0.05uA/mV.

Figure 5.9: Control Driver - OPA Gm

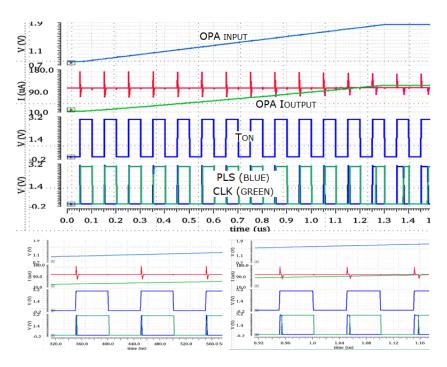

The simulation in Figure 5.10 shows the generation of the PLS and CLK pulses. An input voltage of the OPA causes an output current, which modulates the PLS pulses depending on its value. The CLK pulses are the difference between Ton and PLS.

34 Control Driver

Figure 5.10: Control Driver - PLS Generator Block Simulation

Figure 5.11 shows the simulation of the PLS soft start. At the beginning the pulses, too tight to effectively drive the driver, gradually grow thanks to the closed loop control. The simulation frequency is 10MHz.

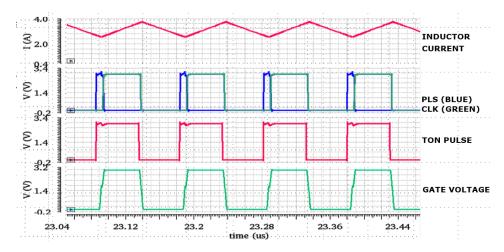

In Figure 5.12 a more detailed simulation of Inductor Current, PLS and CLK Pulses,  $T_{ON}$  and DMOS gate voltage. It is interesting to observe how the gate voltage of the DMOS reaches 3V before being abruptly stopped.

Figure 5.11: PLS Pulses Soft Start - 10 MHz Frequency

Figure 5.12: PLS and CLK Pulses - 10 MHz Frequency

36 Control Driver

# Chapter 6

# Current Sense and Control Logic - PVT Simulations

#### 6.1 Current Sense

Knowing the load conditions is essential in all applications. In DC-DC Converters normally at least the load voltage and/or the load current informations are brought to the control circuit. In this Buck Converter, having to power a LED, we only need to know the current.

To monitor the current, an external Sense Resistor referred to ground and in series with the load is normally used. The voltage drop across it is the feedback signal for the control circuit. This solution is simple and has the advantage of monitoring the current throughout the all period, but this clearly maximizes the power consumption, especially when dealing with a high current LED (e.g. 3A). It also increases the complexity of the board in terms of components, connections, assembly.

When the sense resistor is connected to Ground, additional disadvantages especially in automotive arise from the fact that the LED won't be directly grounded.

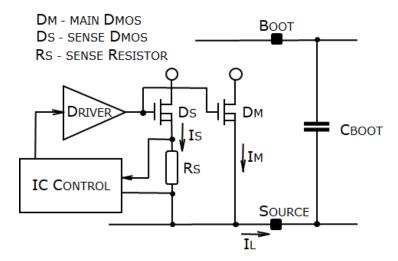

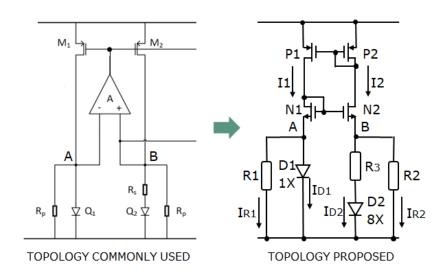

For these reasons and thanks to the Infineon technology it was decided to integrate the current sense. The sensing used is shown in Figure 6.1.

The "Power DMOS" is divided into two DMOS of different sizes. The smallest (SenseDMOS) with the Rsense in series is the effective current sensing as the voltage drop across the resistor constitutes the feedback for the control circuit. The Rsense must therefore have a value such as to generate a measurable signal for the control circuit, and at the same time limit the voltage drop with respect to the Vds of the SenseDMOS in order to find a good compromise between the feedback signal and the current splitted in the two DMOSes as close as possible to the ratio of their areas.

If with K we indicate the ratio between the sensing current  $I_S$  and the total current  $I_L = I_S + I_M$ , we can write in the ideal case taking into account that the area of  $D_S$  in the developed Buck Converter is 15% of the total DMOS:

$$K_I = I_S/I_L = \frac{A_S}{A_M + A_S} = \frac{1/R_{DSS}}{1/R_{DSS} + 1/R_{DSM}} = \frac{0.15}{0.15 + 0.85} = 0.15$$

(6.1)

In the real case in series to  $M_S$  there is the resistance  $R_S$ , and this causes a deviation from the Ideal case. Thus

$$K_R = I_S/I_L = \frac{1/(R_{DSS} + R_S)}{1/(R_{DSS} + R_S) + 1/R_{DSM}}$$

(6.2)

The Current Sense values at ambient temperature are:

$$R_{DSM} = 90m\Omega$$

$R_{DSS} = 510m\Omega$   $R_S = 100m\Omega$  (6.3)

$$K_R = I_S/I_L = \frac{1/(510m\Omega + 100m\Omega)}{1/(510m\Omega + 100m\Omega) + 1/90m\Omega} = 0.128$$

(6.4)

Because the resistance  $R_S$ ,  $K_R$  is affected by a deviation of 15% and this systematic error must be taken into account during the design.

Figure 6.1: Current Sense

Looking at the Figure 6.1 this structure has the drawback that being Rs in series with Ds, the Gate charging current flows through Rs generating a high peak current that causes an error in the measurement of the load current (Figure 6.2). To avoid a wrong feedback this peak has to be masked.

Figure 6.2: Peak Gate Current Superimposed on Is

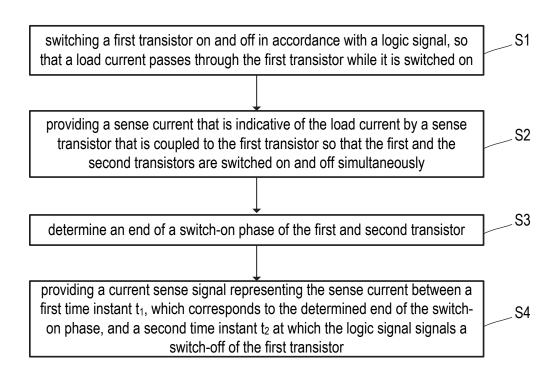

With the current sense in series to the DMOS it is possible to read the current only during  $T_{ON}$ , and during  $T_{OFF}$  the circuit is blind. For this reason it has been adopted a control topology based on the fixed  $T_{OFF}$ . Even reading the current during  $T_{ON}$  only, the Control Circuit developed allows to control the average load current regardless of the duration of  $T_{ON}$  and  $T_{ON}$ .

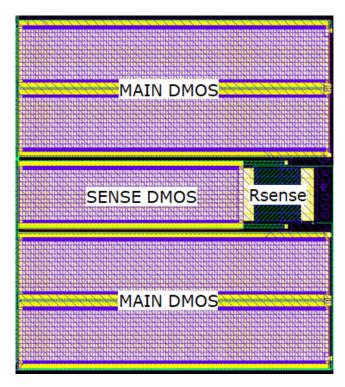

The Main DMOS consists of four equal fingers coupled two by two with the Sense DMOS and Rsense in between. Since the sense DMOS is central and his size is comparable with a DMOS finger, a good matching is guaranteed (Figure 6.3)

Figure 6.3: DMOS and Current Sense Layout

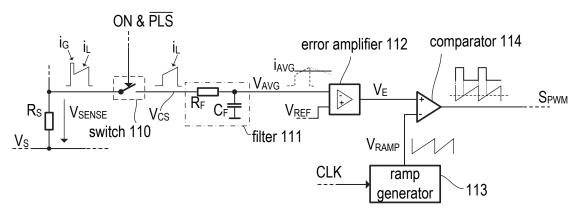

# 6.2 Control Logic

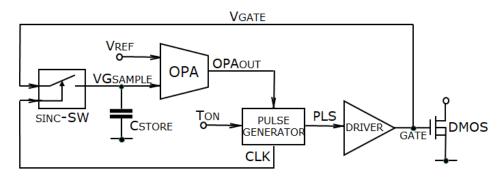

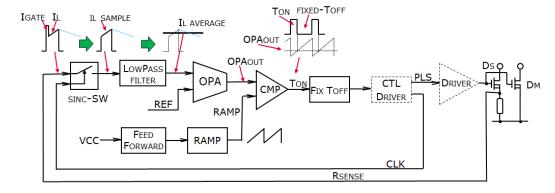

The purpose of the developed buck converter is to control the average current supplying the LED. The control circuit loop is shown in Figure 6.4. The 'CTL Driver' and 'Driver' blocks are shown in dotted line as they are described in the previous chapter.

The signal provided by the  $R_{SENSE}$  can be considered the control input, it consists as already mentioned of the voltage signal generated by the current flowing in  $D_S$  with superimposed the peak of the  $D_S$  gate charging current. This pulse is fundamental for the operation of the circuit, but for the LED current control it represents a source of error and must be removed. Another risk is the tripping of current protection. Since the gate current spike is in phase with PLS pulse, the complementary CLK pulse generated by the "CTL Driver" block is used to synchronise the sampling switch and remove the spike.

The voltage signal across  $R_{SENSE}$ , sampled through "Sinc-SW" and cleaned of the gate spike, becomes a trapezoidal signal proportional to the current in the load during  $T_{ON}$ . The load current during  $T_{OFF}$  cannot be read with the implemented

Current Sense, but must necessarily be trapezoidal in shape with the base length defined by the  $FixT_{OFF}$  block, and it connects two successive  $T_{ON}$  trapezoids.

The trapezoidal signal at the switch output passes through the "Low Pass Filter" Block and is transformed into the DC signal  $I_{L-AVERAGE}$  representing the average current through the LED

$I_{L-AVERAGE}$  is compared by OPA with the load current reference  $R_{EF}$  to generate the comparator first input. The other input is a triangular ramp modulated by VCC via the "Feed Forward" function. The comparator transition determines the  $T_{ON}$  end and the beginning of  $T_{OFF}$ .

The "CTL Driver" block provides the CLK and PLS signals with which the Driver is driven.

Figure 6.4: Buck Converter Control Loop

#### 6.3 10 MHz Buck Converter Simulations

This section shows some simulations of the 10MHz Buck Converter version. The 1MHz and 4MHz versions show similar behaviour.

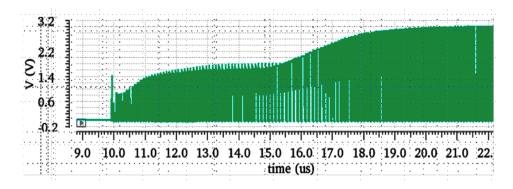

The DMOS gate soft start is shown in Figure 6.5. The effect of the closed loop control in the Control Driver block is evident. the PLS pulse starts with a very narrow pulse and is widened until the DMOS gate reaches 3V.

Figure 6.5: DMOS Gate Voltage Soft Start

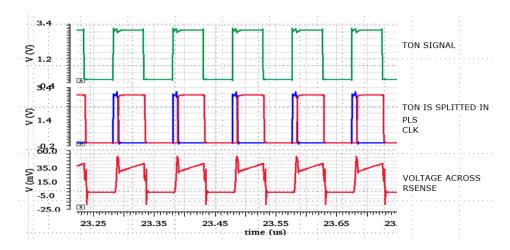

In Figure 6.6 are shown the  $T_{ON}$  pulse generated by the Control Driver and its division into PLS and CLK pulses. The last row is the voltage across  $R_{SENSE}$  where the peak of the gate charge is clearly visible.

Figure 6.6:  $T_{ON}$ , PLS, CLK Pulses and  $R_{SENSE}$  Voltage

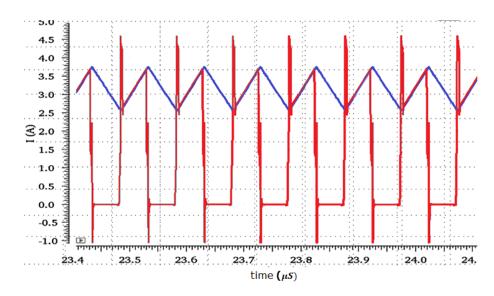

In Figure 6.7 the inductor current is compared with the  $R_{SENSE}$  current appropriately scaled

Figure 6.7: Inductor and  $R_{SENSE}$  Current (Scaled)

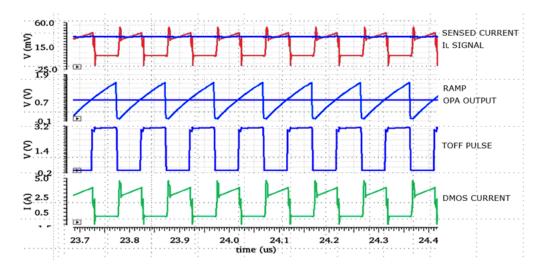

In Figure 6.8 several control circuit signals are shown.

The first row compares the voltage across  $R_{SENSE}$  with the  $I_L$  signal at the output of the Low Pass filter. Even though the current is read only at the  $T_{ON}$ , a signal proportional to the average load current is obtained.

In the second row there is the comparison between the triangular ramp and the OPA OUT. The intersection of the two curves defines the start of  $T_{OFF}$  whose duration is 60nS (third line). The last line shows the total current of the two DMOSes.

Figure 6.8:  $R_{SENSE}$  voltage versus  $I_L$ , Ramp Signal Versus  $OPA_{OUT}$ ,  $T_{OFF}$  Pulse, DMOS Current

# 6.4 4 MHz Buck Converter PVT (Process, Voltage, Temperature) Simulations

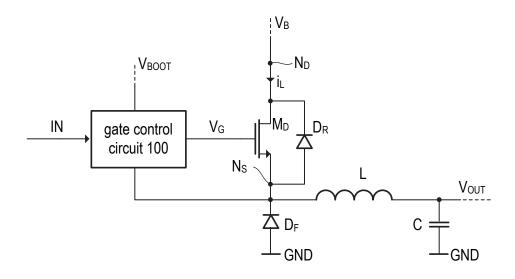

Since the 4MHz switching frequency device is the most commercially attractive, we show PVT simulations of the device in the complete buck conveter system, including load and discrete elements (Figure 1.7).

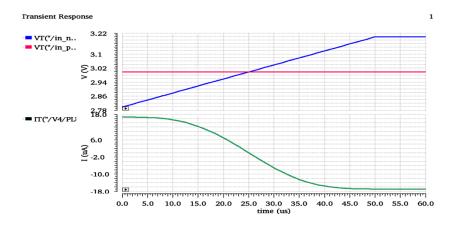

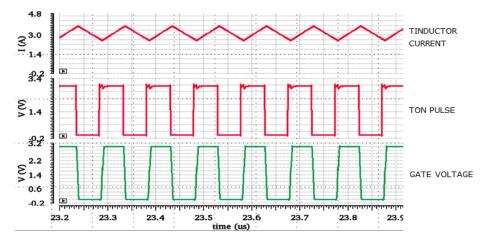

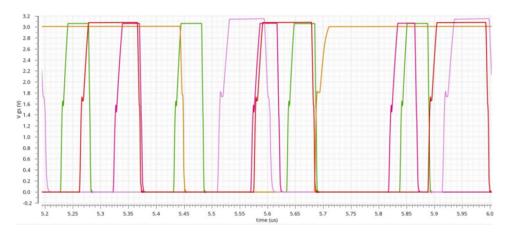

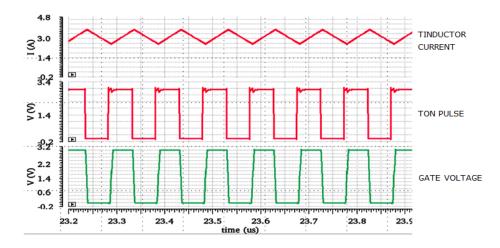

Figure 6.9 shows the load current, the  $t_{ON}$  pulse and the  $V_{GS}$  on DMOS in typical case:  $V_{CC}$ =12V, ambient tempeature and load current 3A.

Figure 6.9: 4 MHz Simulation - Typical Case

The DMOS  $V_{GS}$  shape is fundamental as it represents a summary of the correct operation of the closed loop driver proposed in this work.

It is thanks to this innovative driver that the DMOS gate reaches 3V an order of magnitude faster than conventional drivers, allowing high switching frequencies.

PVT simulations are performed by crossing extreme operating conditions: battery voltage (7V/12V/18V), temperature ( $-40^{\circ}C/27^{\circ}C/150^{\circ}C$ ) and process (min/max/max-min/min-max).

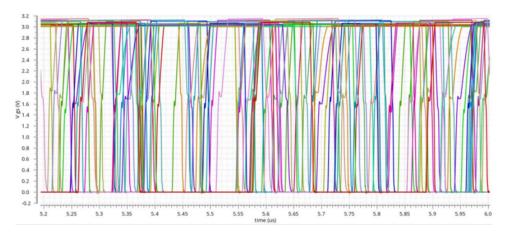

Figure 6.10 shows an overview of the PVT simulations of  $V_{GS}$ . It can be seen how the  $V_{GS}$  reaches the value of 3V almost in a straight line and then abruptly stopped.

Figure 6.10: 4 MHz PVT Simulation -  $V_{GS}$

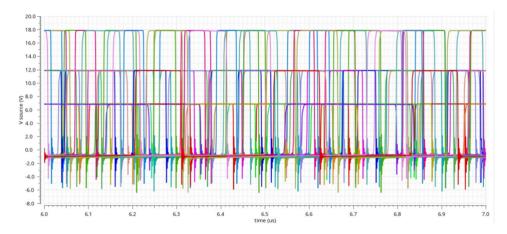

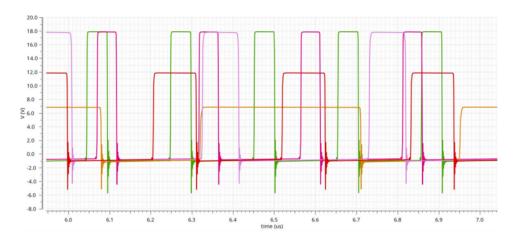

Figure 6.11 shows an overview of the PVT simulations of the square wave voltage on Source PIN.

$V_{SOURCE}$  and  $V_{GS}$  are correlated in that a fast DMOS switch-on implies a fast transition of the Source pin between GND and VCC. In Figure 6.11 in addition to the quick transition the three simulated supply voltages (7V,12V,18V) are evident.

Figure 6.11: 4 MHz PVT Simulation -  $V_{SOURCE}$

In figure 6.12 and figure 6.13 five of the previous simulations are shown to better highlight the transitions of  $V_{GS}$  and  $V_{SOURCE}$

Figure 6.12: 4 MHz PVT Simulation Zoom -  $V_{GS}$

Figure 6.13:  $4~\mathrm{MHz}~\mathrm{PVT}~\mathrm{Simulation}~\mathrm{Zoom}$  - Source

# Chapter 7

# Layout

#### 7.1 Buck Converters Layout

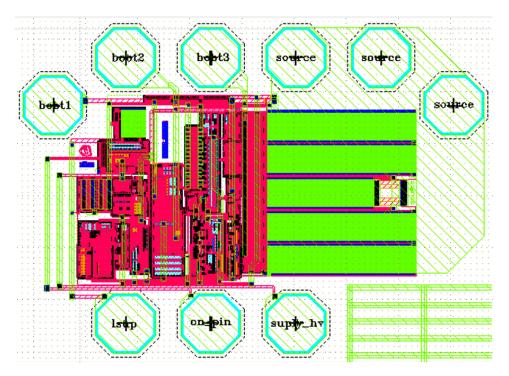

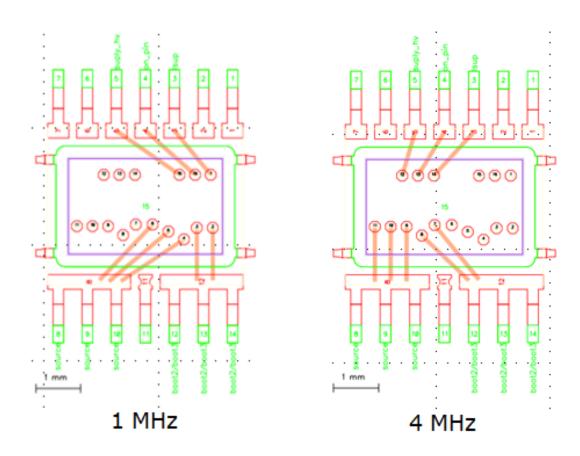

Since a small silicon rectangle has been reserved for us in a development silicon lot we want to diffuse the three Buck Converters, assemble and measure them in the laboratory, we therefore layouted the three devices. For reasons of practicality and time, we first designed the 10MHz version and then derived the 1MHz and 4MHz versions with a limited number of changes.

The layout is shown in Figure 7.1. It is clearly visible that this is a prototype as development time prevailed over area optimisation. In fact, not being a production device where saving area is essential, care was taken to do it within the assigned time. In a development lot, it is crucial to keep to the schedule as different groups come in to test their ideas, hypotheses, circuits, etc., and a delay becomes a delay for everyone.

Looking at the layout Figure 7.1, the Power DMOS with the sensing is on the right, while the control and auxiliary circuitry are in the left half. The PADs are outside the circuitry and not embedded in it as is usual in the production chips. In the lower part are the PADs 'lsup' (GND), 'on-pin' (ON) and 'supply-hv' (signal VCC). In the upper part there are 6 PADs divided into groups of three. The three on the right are in parallel and connected to the Main DMOS Source and the  $R_{SENSE}$  resistor. At the top left are the three PADs 'Boot1', 'Boot2' and 'Boot3'. Externally they are all connected to Bootstrap capacity, while internally they feed different circuits so that disturbances from the noisiest circuits do not affect quieter circuits.

The power VCC is the package lead-frame to which the substrate is connected. The substrate coincides with the DMOS Drain.

46 Layout

Figure 7.1: 1MHz, 4MHz, 10MHz Buck Converter Layout

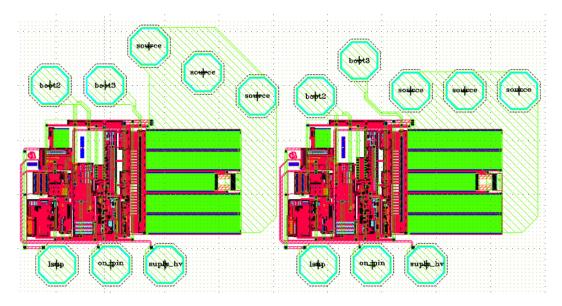

Unfortunately, the silicon area assigned to us is not sufficient to place all three layouts, so it was decided to place two in this "development lot" and the third in the next one.

In this run, the 1MHz and 4MHz versions were chosen, however, it was necessary to reduce the Bootstrap PADs from three to two and to change their position. The Figure 7.2 shows the layout of our silicon rectangle.

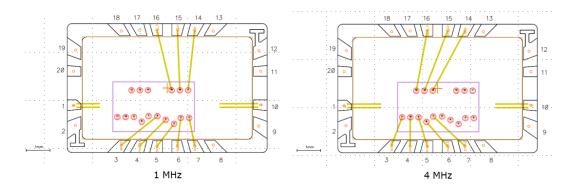

In addition to the silicon layout, the Bonding Diagram layout for the plastic and ceramic packages of both devices must also be prepared (Figure 7.3 and Figure 7.4).

The packages of devices in production are almost always plastic, so it is essential to test the device in its final environment. It is in fact the device in the plastic packaging subjected to reliability tests, and this requires assembly in the production lines, often located in Far East. Clearly, this is not a fast process and the time required for their availability is often a couple of months.

For initial measurements, ceramic packages are therefore used, which are frequently inferior in performance, but as they are assembled on site they are available in a couple of days or so.

Figure 7.2: 1MHz, 4MHz, Buck Converter Layout in Silicon Test Chip

Figure 7.3: 1MHz, 4MHz, Plastic Package Bonding diagram

48 Layout

Figure 7.4: 1MHz, 4MHz, Ceramic Package Bonding Diagram

At the time of writing, the two devices are in diffusion. Wafer out is planned for February 2023.

# Chapter 8

# PCB Design

## 8.1 Introduction

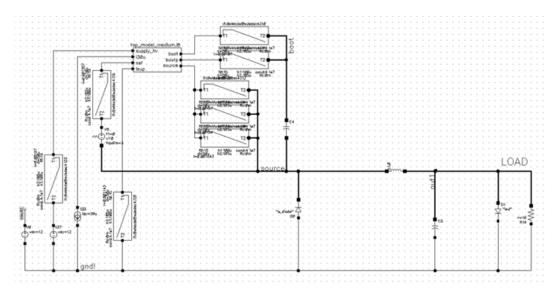

While the devices are under diffusion, the PCB for testing the devices in laboratory must be prepared. This phase also requires the use of the simulator. It is, however, a simulator oriented towards the development of printed circuit boards, which is necessarily different from those used for the development of integrated circuits.

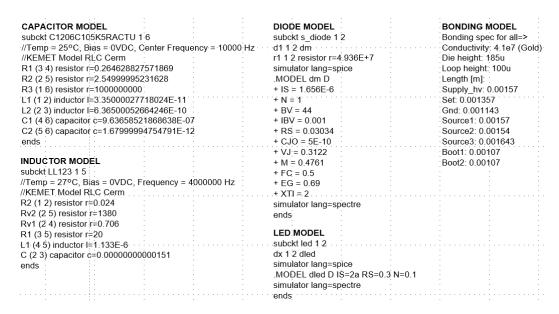

The PCB is designed considering the complete system, so the top view of the device including bonding wires and Spice models of the external components are used (Figure 8.1 and Figure 8.2)

Figure 8.1: PCB Schematic with Real Components

50 PCB Design

Figure 8.2: External Components Model

### 8.2 PCB Simulations and Development

The PCB was developed for the 1 MHz and 4 MHz devices currently in diffusion, and for reasons of practicality, a single board was developed that is suitable for both chips. The PCB simulations show that the complete application with real components is in good agreement with what was seen in the simulations for the silicon development.

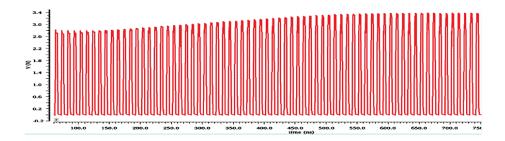

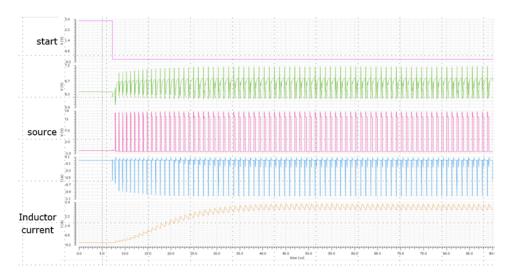

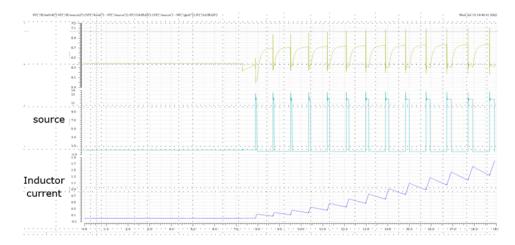

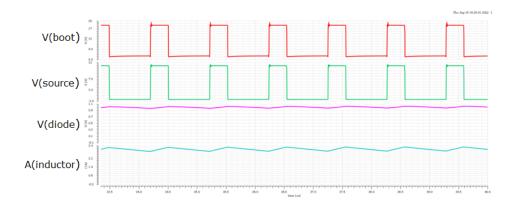

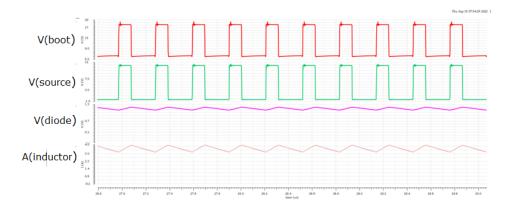

Figure 8.3 and Figure 8.4 show the startup phase, while Figure 8.5 and Figure 8.6 show the two applications under stationary conditions.

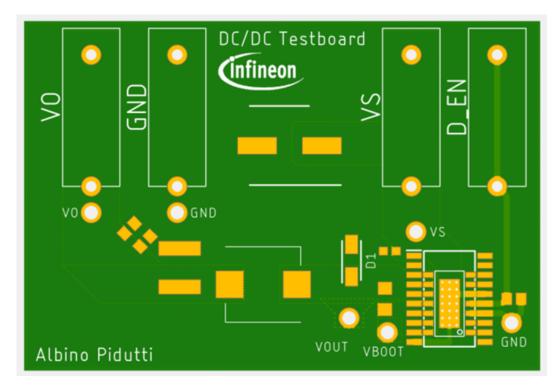

The printed circuit board suitable for both devices is shown in Figure 8.7

Figure 8.3: PCB Startup Simulation - Frequency 1 MHz

Figure 8.4: PCB Startup Simulation - Frequency 1 MHz - Zoom

Figure 8.5: PCB Steady State Simulation 1 MHz

Figure 8.6: PCB Steady State Simulation 4 MHz

52 PCB Design

Figure 8.7: PCB - Test Board

# Considerations About Bandgap

Probably the first Bandgap structure widely used in Integrated Circuits was the one based on the Brokaw cell (Figure A.1) [42].

Figure A.1: Brokaw Cell

The amplifier forces the equality of the voltage drops on the resistance  $R_3$  and  $R_4$ , so that the two branches have the same current  $I_1=I_2=I$ . Being  $Q_2=n\,Q_1$  and having the same base voltage between the emitters  $Q_1$  and  $Q_2$  there will be a voltage equal to

$$\Delta V_{BE} = V_T \ln(n)$$

for n=8 at 25°C  $\Delta V_{BE} = 52mV$  (A.1)

from the Figure A.1

$$2R_1I + R_2I + V_{BE} = V_{REF}$$

(A.2)

$$= (2R_1/R_2 + 1) \Delta V_{BE} + V_{BE} = V_{REF} \tag{A.3}$$

The voltage  $V_{REF}$  is a combination of  $V_{BE}$  and  $\Delta V_{BE}$  The similarity with the formula obtained in chapter 4 and reiterated here is evident.

$$(V_{BE} + \Delta V_{BE}/K) * R_4/R_1 = V_{ref} \tag{A.4}$$

Both circuits by suitably mixing the PTAT and CTAT part obtain a constant temperature reference.

The Brokaw cell has two equilibrium points, one unstable at the origin and one table at the working point. So just move from the origin to automatically end up on the stable equilibrium point (Figure A.2).

Figure A.2: The Two Equilibrium Points in Brokaw Cell

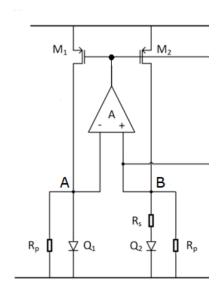

Often in integrated circuits the Bandgap structure shown in Figure A.3 is preferred. The bandgap based on the Brokaw cell having a telescopic structure requires a power supply voltage higher than a parallel structure like the circuit of Figure A.3.

As shown in chapter 4, in the parallel topologies the points on the line  $(0 - Vt_{D2})$  are points of stable equilibrium. Often the starter is a timed circuit activated at the IC start-up that brings the bandgap beyond the operating point and then naturally returns to it.

Figure A.3: Often Used Bandgap Structure

Frequently the parallel structures make use of OPAMP to balance points A and

B. This implies the use of a compensation network and relative stability study.In this work we propose the Bandgap shown in the Chapter 4 "Auxiliary BlocksBandgap" which for convenience we replicate in Figure A.4.

Figure A.4: Buck Converter Bandgap

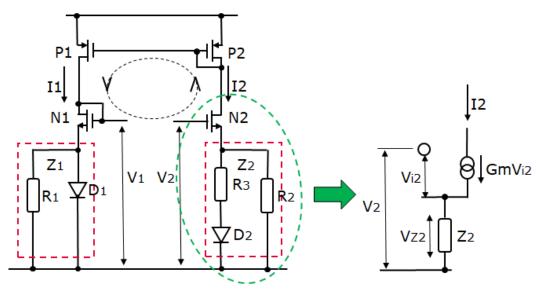

This is also a parallel topology but does not use OPAMPs to define points A and B, being this topology intrinsically stable as demonstrated below.

To calculate the stability we need to open the loop composed of N2-P2-P1-N1 as shown in Figure A.5. Let's call  $Z_1 = R_1 \parallel D_1$  e  $Z_2 = R_2 \parallel (R_3 + D_2)$ . Considering the DMOS simplified equivalent circuit we write

$$V_2 = V_{i2} + V_{z2} = \frac{I_2}{G_{m2}} + I_2 Z_2 = I_2 \left( \frac{1}{G_{m2}} + Z_2 \right)$$

(A.5)

$$I_2 = \frac{V_2}{1/G_{m2} + Z_2} \tag{A.6}$$

with the same procedure for the left half circuit we obtain