## Dipartimento di / Department of

Fisica 'G.Occhialini'

Dottorato di Ricerca in / PhD program FISICA E ASTRONOMIA Ciclo / Cycle XXXV

# INTEGRATED READOUT SYSTEMS FOR PARTICLE DETECTORS

Cognome /Surname Shah Nome / Name Syed Adeel Ali

Matricola / Registration number 863653

Tutore / Tutor: Marcello De Matties

Supervisor: Andrea Baschirotto

Coordinatore / Coordinator: Stefano Ragazzi

ANNO ACCADEMICO / ACADEMIC YEAR 2022/2023

•

.

# Contents

| $\mathbf{A}$ | bstra | act                                         | i   |

|--------------|-------|---------------------------------------------|-----|

| 1            | Cha   | apter 1: Introduction                       | 1   |

|              | 1.1   | The Large Hadron Collider                   | 1   |

|              | 1.2   | The ATLAS Experiment                        | 3   |

|              |       | 1.2.1 Detector Components                   | 5   |

|              |       | 1.2.2 Trigger and Data Acquisition System   | 8   |

|              |       | 1.2.3 Data Taking and Analysis              | 9   |

|              | 1.3   | Towards Higher Luminosity                   | 10  |

|              |       | 1.3.1 LHC Upgrade                           | 10  |

|              |       | 1.3.2 ATLAS Upgrade Projects                | 10  |

|              | 1.4   | Electronic for the physical experiments     | 11  |

|              |       | 1.4.1 State Of The Art MDT AFE              | 12  |

| <b>2</b>     | Cha   | apter 2: FEE Design Overview                | 14  |

| -            | 2.1   |                                             | 14  |

|              | 2.2   |                                             | 16  |

|              | 2.3   |                                             | 18  |

|              |       | -                                           | 18  |

|              |       | 2.3.2 Shaper                                | 20  |

|              |       | 2.3.3 Discriminator                         | 22  |

|              |       | 2.3.4 SLVS Driver                           | 22  |

|              | 2.4   | Programmable Functional Parameters          | 25  |

|              | 2.5   | Serial data I/O and programmable parameters | 26  |

|              | 2.6   | Front End Electronics Design- V2            | 28  |

|              |       | 2.6.1 New SLVS Design                       | 28  |

|              |       | 2.6.2 Test Point Monitors                   | 29  |

| 3            | Cha   | apter 3: Design Layout                      | 31  |

|              |       |                                             | ~ ~ |

| 4            |       | 1                                           | 35  |

|              | 4.1   | Simulations in the Time Domain              | 35  |

|              | 4.2   | Simulations in the Frequency Domain         | 37  |

| <b>5</b>     | Cha   | apter 5: Measurements                       | 41  |

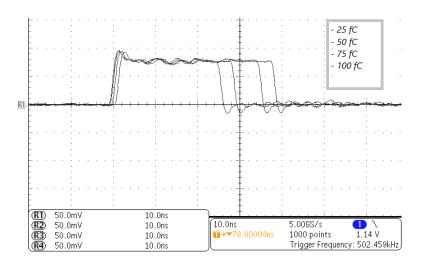

|              | 5.1   | Time-Over-Threshold                         | 41  |

|              | 5.2   | Channel Mode Selection                      | 41  |

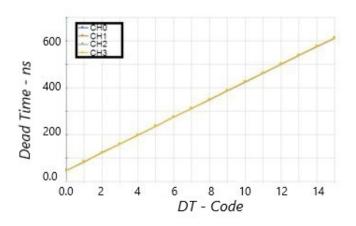

|              | 5.3   | Dead Time Measurement                       | 42  |

|              | 5.4   | Threshold Scans                             | 42  |

| 6 | Cha   | pter 6  | : Paper                                                       | 45 |

|---|-------|---------|---------------------------------------------------------------|----|

|   | 6.1   | Paper   |                                                               | 45 |

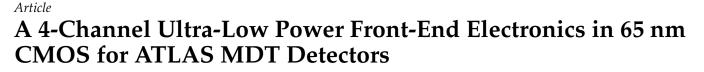

|   |       | 6.1.1   | A 4-Channel Ultra-Low Power Front-End Electronics in 65nm     |    |

|   |       |         | CMOS for ATLAS MDT Detectors                                  | 45 |

|   |       | 6.1.2   | A 4-channel front-end electronics for muon drift tubes detec- |    |

|   |       |         | tors in 65 nm CMOS technology                                 | 45 |

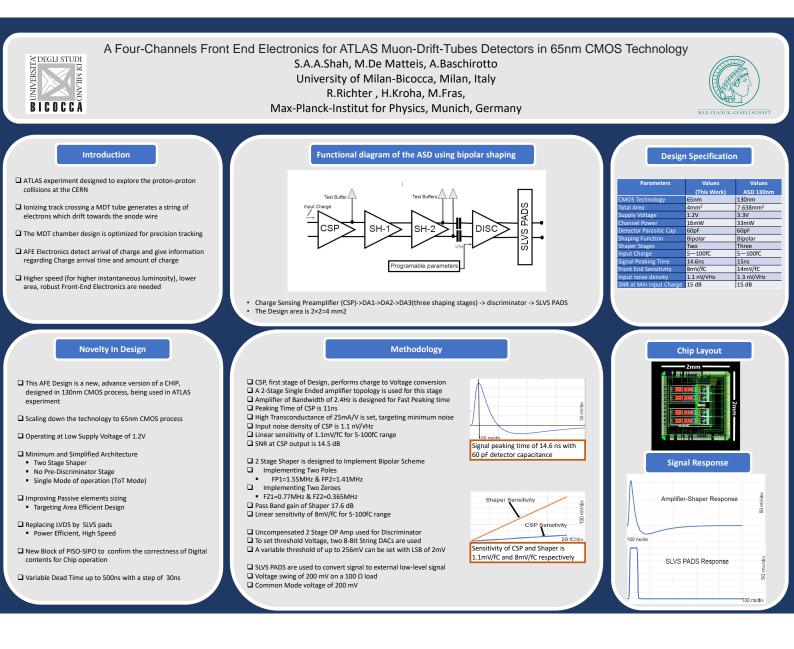

|   | 6.2   | Poster  |                                                               | 64 |

|   |       | 6.2.1   | TWEPP 2021                                                    | 64 |

|   |       | 6.2.2   | TWEPP 2022                                                    | 64 |

| 7 | Con   | clusior | lS                                                            | 67 |

| A | cknov | vledgm  | nent                                                          | 71 |

# List of Figures

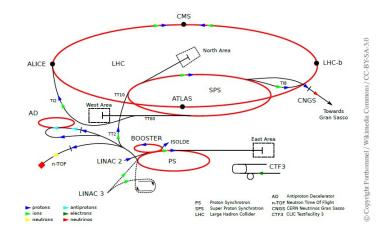

| 1               | The CERN accelerator complex                    | 3 |

|-----------------|-------------------------------------------------|---|

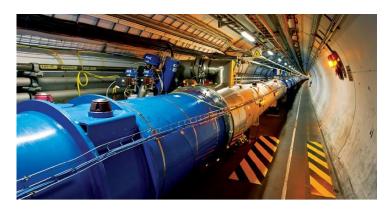

| 2               | Large Hadron Collider (form CERN [1])           | 3 |

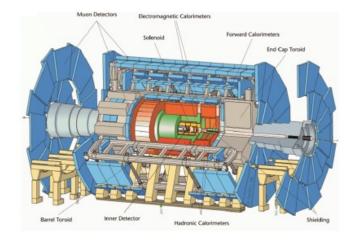

| 3               |                                                 | 4 |

| 4               |                                                 | 4 |

| 5               |                                                 | 6 |

| 6               | The ATLAS calorimeter system [2].               | 3 |

| 7               | The ATLAS Muon Spectrometer [2].                | 3 |

| 8               | Schematic of the first level (L1) trigger [2].  |   |

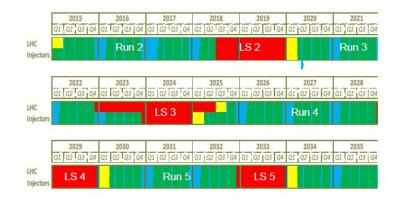

| 9               | CERN LHC and HL-LHC schedule [15].              | - |

| 10              | Photo of ATLAS Detection System[2]              |   |

| 11              | Section of MDT tube                             |   |

| 12              | Simplified Scheme of Muons Detection system[32] | 6 |

| $13^{}$         | ASD Single Channel Schematic                    |   |

| 14              | Scheme of a Charge Sensitive Preamplifier       |   |

| 15              | Scheme of OpAmp used                            |   |

| 16              | Shaper 1                                        |   |

| 17              | Shaper 2                                        |   |

| 18              | Scheme of OpAmp used                            |   |

| 19              | Scheme of OpAmp used                            |   |

| 20              | String DAC and Decoder                          |   |

| 21              | SLVS Block Diagram                              |   |

| 22              | SLVS Transistor Schematic                       |   |

| 23              | Dead Time VS Dead Time code                     |   |

| $\overline{24}$ | Serial Data Interface                           |   |

| 25              | SLVS Block Diagram                              |   |

| 26              | SLVS Schemaitc                                  |   |

| 27              | Test Point Buffer                               |   |

| 28              | Channel Layout                                  | 1 |

| 29              | Pad Ring.                                       | 2 |

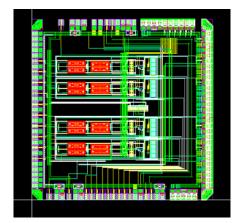

| 30              | Core Layout                                     | 3 |

| 31              | Chip Layout Design                              | 3 |

| 32              | FEE package Layout Design                       |   |

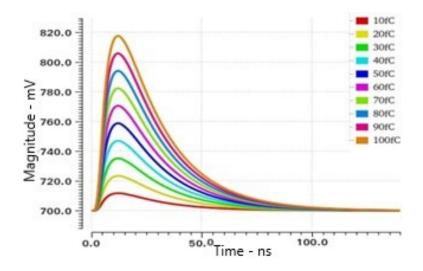

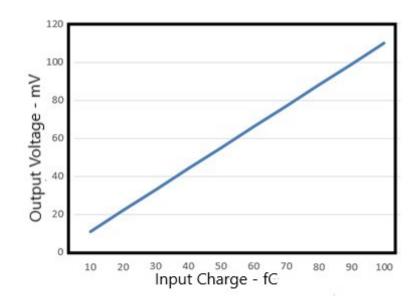

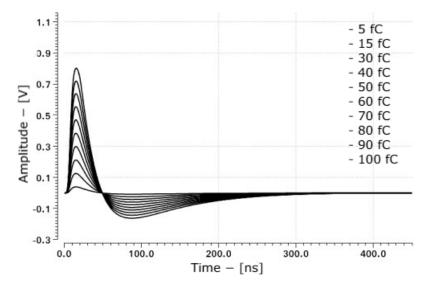

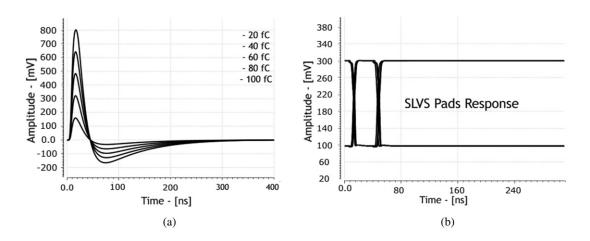

| 33              | CSP Transient Response                          | 3 |

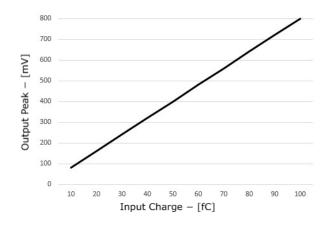

| 34              | CSP Sensitivity                                 | 3 |

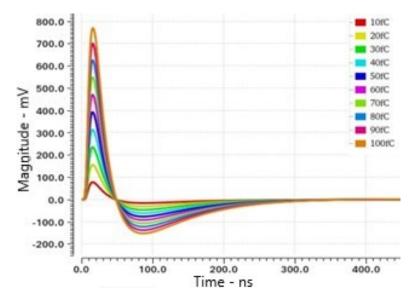

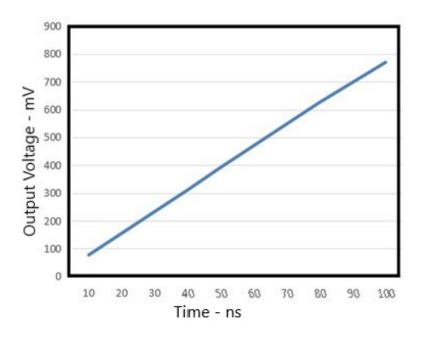

| 35              | Shaper Transient response                       | 7 |

| 36              | Shaper Sensitivity                              | 7 |

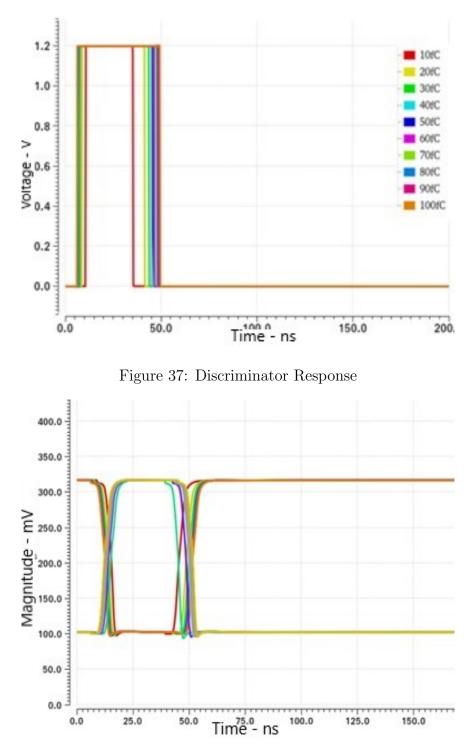

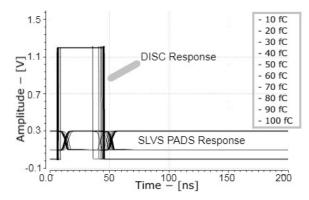

| 37              | Discriminator Response                          | 3 |

| 38              | SLVS Drivers Response                           | 3 |

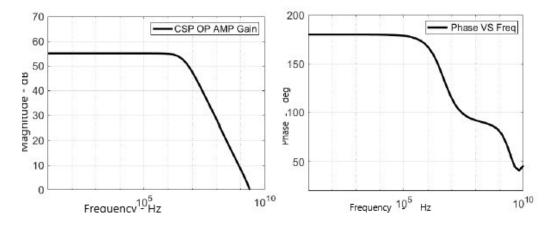

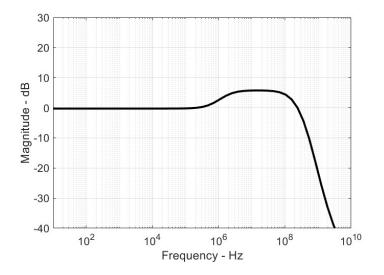

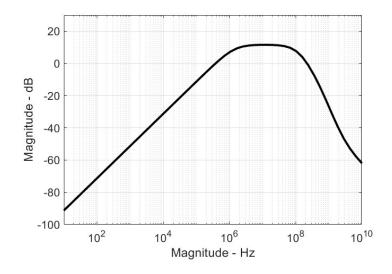

| 39              | CSP OP-Amp Frequency Response                   | 9 |

| 40              | CSP close loop frequency response               | 9 |

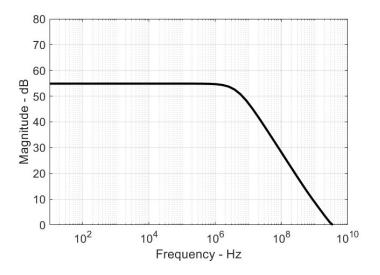

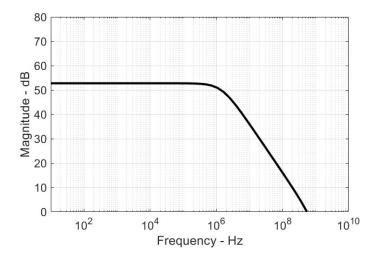

| 41              | Shaper OP-Amp Frequency Response                | 9 |

| 42              | Shaper-1 close loop frequency response          | ) |

| 43              | Shaper-2 close loop frequency response          | ) |

| 44              | Time Over Threshold                             | 2 |

| 45              | Dead Time measurement                           | 2 |

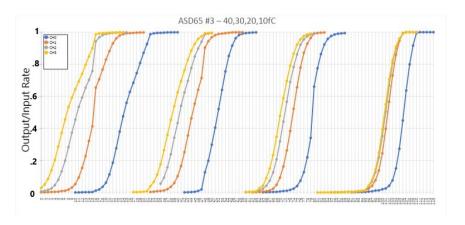

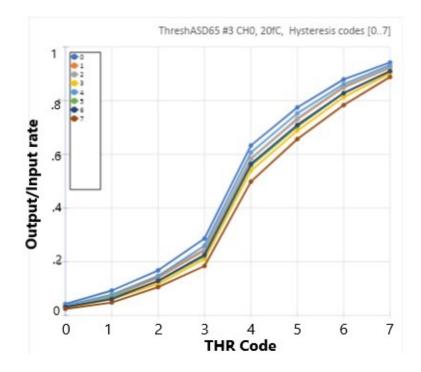

| 46              | Threshold scan for channels of FEE chip 43      | 3 |

| 47 | Threshold scan and effect of Hysteresis | 43 |

|----|-----------------------------------------|----|

|    | FEE chip                                |    |

# List of Tables

| 1 | Nominal design machine parameters of the Large Hadron Collider.  |    |

|---|------------------------------------------------------------------|----|

|   |                                                                  | 2  |

| 2 | Operating parameters of MDT chambers with large and small tubes. | 16 |

| 3 | CSP W/L and Trans-conductance value.                             | 20 |

| 4 | Shaper Impedance Network components value                        | 22 |

| 5 | Programable Parameter of FEE Chip                                | 25 |

| 6 | Serial interface signal lines                                    | 28 |

| 7 | Serial interface instruction encoding.                           |    |

| 8 | Main Parameters of Package                                       |    |

# Abstract

Increasing demand for high rate detectors in modern High-Energy-Physics (HEP) experiments is generating many technological challenges. Particularly, the particle detectors utilized in HEP experiments requires efficient readout electronics systems that can cope with the challenges faced due to the upgrade in HEP experiments. CMOS integrated circuits, widely used technology, is a common choice for readout chip based on reliability, cost reduction and performance improvement factors.

In this thesis, a general information of the experiment along with the upcoming challenges due to expected upgrade in the experiment are presented and a new readout electronic system, targeting a significantly power efficient, are efficient design, with a promising performance targetting to replace the existing readout electronics is presented. The first part of this thesis presents the LHC experiment information and the classical readout electronics, fabricated in CMOS 130nm, used for it.

Chapter 2 and 3 of this thesis presents the new readout chip, Front End Electronics for Monitored Drift Tube in a long sustainable technology, 65nm CMOS. This readout system has been specifically designed for Muon Drift Chambers matching the performance parameters of the existing readout electronics design. After theoretical analysis of the signal processing technique, the implementation of design is presented in detail. The simulations and measurement results are reported in Chapter 4 and 5.

# 1 Chapter 1: Introduction

The main goal of High-Energy Physics (HEP) experiments, carried out at CERN is to study the fundamental constituents of matter in terms of elementary charge particles, their interactions and their secondary products. Part of these phenomena have already been studied and are used to define the Standard Model of matter. In 2012, after 40 years of search, a subatomic particle with the expected properties of the missing paricle, was discovered in 2012 by the ATLAS experiment at CERN. The new discovered particle was later-on confirmed to match the expected properties of a Higgs bosons. The discovery of the Higgs bosons was a major milestone in particle physics. It is considered as the end of decades-long journey of exploration and the start of a new era of studies of this very special particle. The further challenges of CERN project is targeted to provide more details on the new charged particles as Higgs Bosons and neutrinos.

The Large Hadron Collider, world's largest and most powerful particle accelerator, at the CERN works every day for this purpose. It has a superconducting magnetic ring structure able to guide two high-energy particle beams. The high energy particle beams have opposite directions and they travel at light speed. Charged particles are generated from collisions of beams and they are accelerated toward a proper detector. Different detectors are located in different points of the collider. They are organized in shell structures and are designed to detect few topology of particles. Typically, the parameters useful to identify a charged particle are electrical charge, momentum, energy, distance and time of flight.

Detectors design is important but it is performance depends upon efficient electronic read-out systems, to collect and provide the correct required information. A big experiment requires a hard work of scientists, engineers and technicians.

In the last decade, electronics design have become more and more efficient and compact. CMOS integrated solution are preferred because of reliability, cost reduction and performance improvement. Proper and efficient readout electronics design is challenging but not impossible. Some characteristics are directly dependent from the electronic designer and their capability to manage the external parasitic effects, which are unavoidable factors in the experiment, as the parasitic capacitance of the connected detector.

# 1.1 The Large Hadron Collider

The Large Hadron Collider (LHC) at CERN [1] is the most powerful accelerator and collider in terms of luminosity and beam energy upto date. It is located in the same 26.7 km long tunnel as the Large Electron Positron Collider (LEP) which was shut down and decommissioned in 2000.

The tunnel is ring-shaped, consisting of eight arcs and eight straight sections, and is located 45m to 170m below the surface on slightly inclined plane. Two transfer tunnels, 2.5 km long, connect it to the rest of the CERN accelerator complex (see Figure 1) which is used for beam injection.

As a proton–proton collider, the LHC contains two separate vacuum pipes with oppositely oriented magnetic fields for the counter-rotating beams. A "twin bore design" was chosen for the superconducting dipole magnets that keep the beams on circular orbits. In this compact design, the two rings are integrated into the superconducting magnets in the same cryostat. The dipole magnets generate a field strength of up to 8.33 T allowing for a maximum proton beam energy of 7 TeV. The proton beams are divided into 2808 bunches of 1.15.10<sup>11</sup> protons each with 25 ns spacing resulting in a collision rate of 40 MHz at design operation of the LHC.

Of the eight straight sections of the LHC, four of them house the big experiments named as: ALICE, ATLAS, CMS and LHCb. ATLAS [2] and CMS [3] are multipurpose detectors, which contributed in the discovery of the Higgs Boson particle, designed to operate at the design centre-of-mass energy of 14 TeV and luminosity of up to  $L=1.10^{34}cm^{-2}s^{-1}$ .

Main LHC machine parameters are presented in Table 1.

| Parameter                        | Value                                  |

|----------------------------------|----------------------------------------|

| Circumference                    | 26659 m                                |

| Center of Mass Energy            | $14 { m TeV}$                          |

| Luminosity                       | $10^{34} \text{cm}^{-2} \text{s}^{-1}$ |

| Emittance                        | $3.75 \ \mu m rad$                     |

| β                                | $0.55 \mathrm{~m}$                     |

| Bunch Spacing                    | 25  ns (7.5  m)                        |

| No. protons per bunch (at start) | $1.5 \times 10^{-11}$                  |

| Collision crossing angle         | $300 \ \mu rad$                        |

| Average crossing rate            | 31.6 MHz                               |

| RF Voltage (at 7 TeV)            | 16 MV                                  |

| Number of RF Cavities            | 8                                      |

| Number of Dipoles                | 1232                                   |

| Number of Quadrupoles            | 858                                    |

| Dipole operating temperature     | 1.9 K                                  |

| Peak Dipole Field Strength       | 8.33 T                                 |

| Stored beam energy               | 360 MJ                                 |

| Stored energy in magnets         | 11 GJ                                  |

| Typical beam lifetime            | 10 h                                   |

| Synchrotron radiation per beam   | 6  kW                                  |

|                                  |                                        |

Table 1: Nominal design machine parameters of the Large Hadron Collider.

After the achievement of the main goal, the discovery of the Higgs boson in 2012 [4,5] as the last missing particle of the Standard Model, the experiment aims to search for any accessible physics beyond the Standard Model and to perform measurements of the properties of the Higgs boson like coupling strengths to bosons and fermions, total decay width and CP quantum numbers.

LHCb [6] experiment is dedicated to b-hadron physics designed to operate at a lower luminosity of  $L=1.10^{2}$  cm<sup>-2</sup>s<sup>-1</sup>. It performs precision measurements of CP-violation that may help to explain the matter–antimatter asymmetry in the universe and searches for rare B meson decays.

In addition to protons, the LHC can collide lead ions  $(^{208}\text{Pb}^{+82})$  in lead–lead and lead–proton operating modes at a centre-of-mass energy of  $\sqrt{s} = 2.76$  TeV per nucleon. At the high energy densities reached in lead–lead collisions, quarks and gluons are expected to form a colourdeconfined state called quark–gluon plasma. The AL-ICE experiment [7] is devoted to the study of heavy ion collisions at a luminosity of L= $1.10^{27}$  cm<sup>-2</sup>s<sup>-1</sup>.

Figure 1: The CERN accelerator complex.

The four big LHC experiments, mentioned above, share their interaction points with three smaller experiments known as: LHCf, TOTEM and MoEDAL. LHCf [8] consists of two detectors 140m from the interaction point on both side of the ATLAS detector and aims to understand the origin of ultra-high-energy cosmic rays. TOTEM [9] shares the interaction point with CMS and consists of detectors 147m and 220m from the collision point. It is designed for the measurement of the total proton–proton interaction cross section and elastic and diffractive scattering processes. MoEDAL [10], which got approval in 2010, is the newest of the LHC experiments. Its goal is the search for magnetic monopoles and other strongly ionising massive particles.

Figure 2: Large Hadron Collider (form CERN [1]).

## 1.2 The ATLAS Experiment

The ATLAS detector is a multipurpose detector designed to explore a wide range of physics topics. The unprecedented energy and luminosity of the LHC allow for both precision measurements of the Standard Model and searches for any credible new physics processes beyond the Standard Model.

The high interaction rate and luminosity, however, demands for high performance readout electronics in-terms of radiation tolerance, spatial and time resolution. The production cross-sections of most interesting processes are smaller by many orders

Figure 3: Scheme of complex ATLAS Detector[2].

of magnitude than the total inelastic proton-proton cross-section of about 80 mb which is dominated by dijet production. At design luminosity, crossing rate of 40 MHz, each interesting event is accompanied by on average, further, 23 inelastic events. Highly granular, radiation hard detectors and electronics are needed to cope with the high radiation levels and track density to control the effects of overlapping events. As the read-out and storage capacity is limited, a very selective, robust and efficient trigger system is required to arrive at a manageable data volume, without discarding interesting rare events.

High resolution electromagnetic calorimetry is essential for efficient electron and photon detection and precise energy measurement. Hermetic hadronic calorimetry is important for accurate jet and missing transverse energy measurements which are fundamental for many studies.

Figure 4: The superconducting solenoid (blue) and toroid (red) magnet coils [2].

The ATLAS detector scheme shown in Figure 3, is forward–backward symmetric with respect to the interaction point. The individual sub-detectors are arranged in

a cylindrical pattern, around the beam pipe in the central barrel region and in discs, in the so-called end-caps, typical for different collider experiments.

The superconducting magnet system consists of a thin solenoid coil. It surrounds the inner tracking detector with a diameter of 2.5m and a length of 5.3m and three large air-core toroids (one for the barrel and one for each end-cap) in the Muon Spectrometer. The layout of the magnet system is shown in Figure 4.

The ATLAS design uses a right-handed coordinate system. Its origin is at the nominal interaction point, in the centre of the detector, and the z-axis along the beam line. The y-axis is directed upwards and the x-axis points from the interaction point to the centre of the LHC ring. Cylindrical coordinates (r,  $\theta$ ,  $\Phi$ ) are used in the transverse plane.  $\Phi$  is the azimuthal angle around the beam line,  $\theta$  the polar angle and r the radius measured from the beam line. Transverse observables (index  $\tau$ ) are projections into the x-y plane perpendicular to the beam line.

#### 1.2.1 Detector Components

This section briefly describes the sub-detectors of the ATLAS experiment.

#### The Inner Tracking Detector:

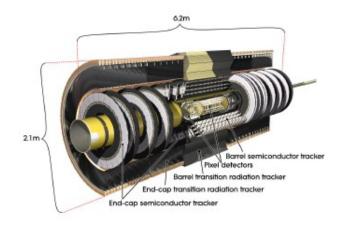

When a p=p collision occurs, around 1000 particles emerge at the LHC, which leads to a high density of tracks in the detector. ATLAS uses a combination of three technologies in the Inner Detector (ID): silicon pixel, micro-strip (SCT) detectors and a Transition Radiation Tracker (TRT) — to achieve the required momentum and vertex resolutions. The ID is immersed in a 2 T magnetic field created by the central solenoid. The design layout of the ID is shown in Figure 5.

The innermost component is the Pixel Detector, and is arranged around the interaction point in three concentric cylinders in the barrel region and the disks perpendicular to the beam line in the end-cap regions. The spatial resolution provided by the Pixel Detector is 10 µm in the transverse plane and 115 µm in the longitudinal direction with respect to the beam line. The innermost detector layer is at a distance of only 5 cm from the beam line and is of especial importance for the measurement of decay vertices needed for b-quark and  $\tau$ -lepton identification as well as for searches for new long-lived discovered particles. The Pixel Detector has a large number of readout channels, approximately 80.4 million.

In a similar pattern but with four layers, the Semiconductor Tracker SCT (Semiconductor Tracker) surrounds the Pixel Detector. It uses silicon micro-strip sensors with an average strip pitch of 80 µm assembled back-to-back with a stereo angle of 40 mrad in each layer to measure track coordinates with a resolution of 17 µm in transverse and 580 µm in longitudinal direction. Both the Pixel and the SCT detectors cover the pseudo-rapidity range  $|\eta| < 2.5$ .

The outermost component of the ID is the TRT. It consists of a 4mm diameter straw drift tubes, made of 35 µm thick Kapton with 31 µm diameter gold-plated tungsten anode wires operated with Xenon/Carbon dioxide/oxygen (70/27/3) gas at 5 to 10 mbar over-pressure. For every track, The TRT provides on average 36 coordinates with a resolution of 130 µm in transverse direction over a pseudo-rapidity range of  $\eta=2$ .

Transition radiation photons from electrons traversing the polypropylene fibres and

Figure 5: The ATLAS Inner Detector [2].

foils with which the straws are interleaved, ionize the enclosed Xenon gas yielding much larger signals than minimum-ionizing particles and thus providing electron identification. The large number of hits per track allows for robust pattern recognition.

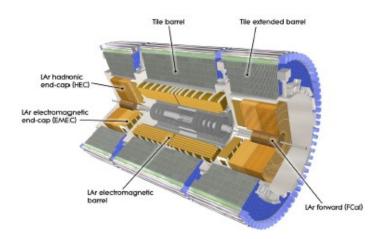

#### Calorimeter:

The ATLAS calorimeter system consists of electromagnetic and hadronic sampling calorimeters covering the pseudo rapidity range  $\eta < 4.9$ . The total thickness of the electromagnetic calorimeters is more than 22 radiation lengths. Approximately 11 nuclear interaction length of the whole calorimeter system sufficiently reduce the punch-through into the Muon Spectrometer.

The high containment of hadrons together with the large  $\eta$ -coverage enables high jet and missing transverse energy resolution which are crucial for a hadron collider experiment. An overview of the calorimeter system is given in Figure 6.

Figure 6: The ATLAS calorimeter system [2].

#### **Electromagnetic Calorimeters:**

The electromagnetic calorimeter uses liquid argon (LAr) as active medium and

lead absorber material in a barrel part and two end-cap parts. The barrel part shares the vacuum vessel with the superconducting solenoid magnet it surrounds minimising the amount of dead material which deteriorates the energy resolution. Each end-cap consists of two coaxial wheels. All parts consist of radially accordion-shaped lead absorber plates and Kapton electrodes. The accordion geometry provides homogeneous azimuthal response and electronics connections at the outer diameter. The absorber plate thickness is optimised for energy resolution as a function of  $\eta$ . For  $\eta < 2.5$ , the electromagnetic calorimeter is segmented into three sections in depth, while in the more forward regions there are only two sections in depth and also the lateral granularity is reduced. In the range  $\eta < 1.8$ , a highly segmented LAr pre-sampler is used to correct for energy loss upstream of the calorimeter.

#### Hadronic Calorimeters:

The hadronic calorimeter consists of a barrel and two end-cap parts augmented by a forward calorimeter. The barrel Tile Calorimeter with its extensions uses steel as absorber and scintillating tiles as active medium and covers the ranges  $\eta < 1.0$  and  $0.8 < \eta < 1.7$ , respectively. Both the barrel and the extended barrels are segmented into 64 modules azimuthally and three sections in depth. The scintillating tiles are read out on two sides by photomultiplier tubes via wavelength shifting fibres. The hadronic end-cap LAr calorimeter is located directly behind the electromagnetic end-cap calorimeter and shares the same cryostat.

It consists of two wheels on each side, each consisting of 32 wedge-shaped modules. Copper plates, 25mm thick in the inner and 50mm thick in the outer wheel, are used as absorber material, separated by 8.5mm wide LAr gaps.

The forward calorimeter shares the cryostats with the end-cap calorimeters and covers the range  $3.1 < \eta < 4.9$ . It is recessed by about 1.2m with respect to the front of the electromagnetic calorimeter in order to reduce neutron albedo into the inner detector. It also utilizes LAr as the active medium and consists of three modules in longitudinal direction. The innermost module enhanced for electromagnetic measurements uses copper absorbers, the other two enhanced for measurements of hadronic interactions use tungsten absorbers. A matrix of longitudinal channels filled with LAr as active medium is embedded into the absorber materials.

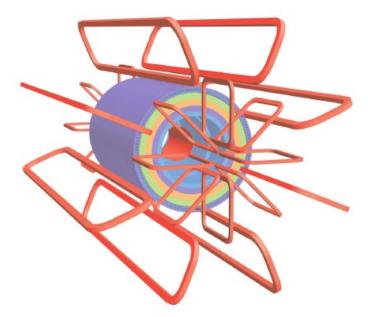

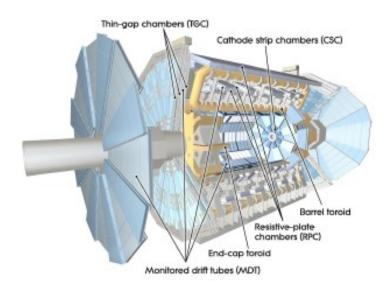

#### The Muon Spectrometer:

The distinctive part of the ATLAS detector is the Muon Spectrometer which defines the overall size of the detector. It has a length of 44m and diameter of 25m. It measures the deflection of muon tracks in the magnetic field generated by large superconducting air-core toroid magnets and is designed to provide a highly efficient muon trigger and high-precision muon momentum measurement up to the TeV scale. It utilizes a position-sensitive detector that records tracks of charged particles, and a magnetic field so that charge and momentum can be recorded from the track curvature. The air-core magnet design minimises the degradation of the momentum resolution due to multiple scattering. An overview of the Muon Spectrometer is given in Figure 7.

The Muon Spectrometer is subdivided into the barrel part ( $\eta < 1.4$ ), where the toroidal magnetic field is provided by the eight 20m long superconducting coils and two end-caps ( $1.6 < \eta < 2.7$ ), where the magnetic field is provided by two separate superconducting toroid magnets. In the transition region between the barrel and

the end-caps ( $1.4 < \eta < 1.6$ ), there is a superposition of the barrel and end-cap toroid fields. While the eight barrel toroid coils are housed in individual cryostats assembled symmetrically around the beam line, the end-cap toroid coils on either side of the detector share a common cryostat. The eight end-cap toroid coils are rotated by  $22.5\theta$  with respect to the barrel toroid coils in order to provide radial overlap and improve the bending power in the transition region (see Figure 1.3). The magnetic field is mostly perpendicular to the muon trajectories and provides a bending power in the range from 1 to 7.5 Tm.

Dedicated detectors for precision tracking and triggering are arranged in three cylindrical layers around the beam axis in the barrel and in three wheels in the end-cap regions. The majority of the precision tracking chambers are Monitored Drift Tube (MDT) chambers which are described in detail in the following chapter as they form the framework of this thesis.

Figure 7: The ATLAS Muon Spectrometer [2].

Only in the inner end-cap layer at large pseudo-rapidity  $(2.0 < \eta < 2.7)$ , where the particle flux is too high for the MDT chambers, Cathode Strip Chambers (CSC) with higher granularity and faster response are used. In total, 1150 MDT chambers with 350 000 drift tubes and 32 CSCs with 31 000 channels cover the pseudorapidity range  $\eta < 2.7$ . Resistive Plate Chambers (RPC) are used as trigger detectors in the barrel region while. Thin Gap Chambers (TGC) are used in the end-caps. Besides providing a fast trigger decision, the trigger chambers provide bunch crossing identification and measurement of the second coordinates of the muon tracks in the direction of the drift tubes of the MDT chambers. The spatial resolution is only on the order of 1 cm.

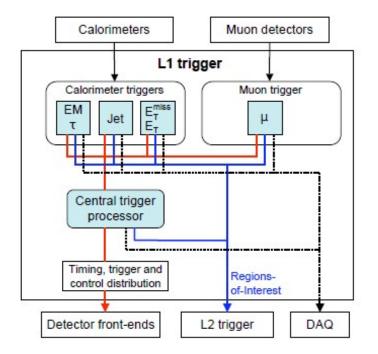

### 1.2.2 Trigger and Data Acquisition System

ATLAS uses a three-level trigger system to minimize the event rate from the 40MHz bunch crossing rate to almost 200 Hz written to tape. The first trigger level (L1) is designed in custom-made electronics. The second (L2) and third (Event Filter)

levels utilizes commercial computer farms. The L1 trigger as shown in Figure 8, takes decisions in a very minute time frame, 2.5µs and reduces the event rate to about 100 kHz. It searches for electrons, high transverse momentum muons, photons, jets and

Figure 8: Schematic of the first level (L1) trigger [2].

$\tau$ -leptons decaying into hadrons as well as for events with large transverse energy. The L1 decision is taken by the Central Trigger Processor (CTP) which also provides selection criteria like passed thresholds and regions-of-interest (RoI) information to the L2 trigger.

The L2 trigger uses the regions-of-interest information provided by the L1 trigger as a starting point for the processing of the full detector information with simple reconstruction programs within the regions-of-interest. It reduces the event rate to about 3.5 kHz with an average processing time of 40ms.

Finally, the last event selection is performed by the third stage, the "Event Filter", which uses the full ATLAS event reconstruction software. It reduces the event rate to 200 Hz with a typical processing time of four seconds per event. With an average event size of 1.3MB, the average output bandwidth is almost 300MB/s.

### 1.2.3 Data Taking and Analysis

During the first period of operation from 2010 to 2012, now called Run 1, the LHC has delivered integrated luminosity of  $L = 5.5 \text{ fb}^{-1}$  at a centre-of-mass energy of  $\sqrt{s} = 7$  TeV and of  $L = 22.8 \text{ fb}^{-1}$  at  $\sqrt{s} = 8$  TeV to the ATLAS and CMS experiments [11].

With these recorded sets of data, the Standard Model (SM) of particle physics has been confirmed in the new energy regime culminating in the discovery of the last missing SM particle, the Higgs boson, in 2012 [4, 5] with a mass of mH  $\approx 125.5$  GeV [12, 13] and rate compatible with the SM prediction.

Researchers have searched alot but no evidence for physics beyond the Standard Model could be confirmed in first period of operation. Second Run of ATLAS experiment is happening at increased centre-ofmass energy of 13 TeV and the search for Physics beyond the standard model is still in process.

An increase of the integrated luminosity is desirable, not only to discover new physics, but also to study the still open questions of the Standard Model like the naturalness or hierarchy problems or the origins of dark matter and of the matter-antimatter asymmetry

Figure 9: CERN LHC and HL-LHC schedule [15].

## 1.3 Towards Higher Luminosity

### 1.3.1 LHC Upgrade

During Run 2, which was planned to last from mid 2015 to mid 2018, the LHC reached its target the design luminosity and energy. After the so-called Phase-I upgrades of the LHC with improvements to the injectors including a new linear accelerator LINAC4 [14] replacing the current LINAC2, the instantaneous luminosity is be doubled to  $2.10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. In this configuration, the LHC will be operated until 2023 and deliver at least 300 fb<sup>-1</sup> of proton–proton collisions to the ATLAS and CMS experiments.

After Phase-II upgrades from 2023 to 2025, the LHC will reach an instantaneous luminosity of  $7.10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> (High-Luminosity LHC or HL-LHC) and deliver 3000 fb<sup>-1</sup> within the following ten years.

### 1.3.2 ATLAS Upgrade Projects

With the increase of the instantaneous luminosity beyond the design value and extended running time, the LHC experiments need to adjust with the higher demands on rate capability, particle multiplicities, radiation hardness and trigger selectivity in order to take advantage of the higher luminosity.

This section gives an overview of planned ATLAS upgrade projects in the coming decade. The goal of the upgrades is to at least maintain and even improve upon the design performance at the higher luminosity.

**Detector Consolidation Phase-0** The biggest upgrade project during the first long LHC shutdown (2013–2014) was the installation of the "Insertable  $\beta$ -Layer"

(IBL), a fourth layer added inside the present pixel detector on a new beam pipe [16]. The IBL enhances the decay vertex reconstruction and hence the b-hadron and  $\tau$ -lepton identification and compensates for deterioration of present pixel detector due to radiation damage.

Another significant upgrade project is the installation of additional muon tracking chambers to improve the momentum resolution in a so far poorly instrumented region of the barrel Muon Spectrometer [17]. A new type of smaller diameter drift tube (sMDT) chambers is used.

**Phase-I Upgrades** The Phase-I upgrades of the Muon Spectrometer in 2018–2019, Figure 9, anticipate necessary improvements for HL-LHC [18]. The main project was the replacement of the inner end-cap layer of the Muon Spectrometer, the so-called Small Wheel, by the New Small Wheel (NSW) using detector technologies with higher rate capability and spatial trigger detector resolution [19].

**Phase-II Upgrades** The Phase-II upgrades are planned for 2022–2024 which will enable efficient operation at HL-LHC conditions for additional ten years to collect collision data corresponding to 3000 fb<sup>-1</sup> [20].

Entire replacement of the inner tracking detector, which reaches the end of its lifetime after 400 fb<sup>-1</sup>, is required. The new tracker has to deal with a much higher track multiplicity from up to 200 interactions per bunch crossing and tolerate more than an order of magnitude higher radiation doses.

To limit the trigger rate without missing interesting events, the selectivity of the L2 trigger has to be reached already at L1. With trigger latencies above 30 µs, inner detector track reconstruction information can be incorporated into the L1 trigger and combined with more complex calorimeter and muon triggers [21]. The low-momentum muon trigger rate can be suppressed by higher momentum resolution of the L1 muon trigger using the high spatial resolution of the MDT chambers [22, 23].

## **1.4** Electronic for the physical experiments

The most important discoveries on the matter components has been developed in the CERN laboratory at Geneva exploiting the world's largest and most powerful particle accelerator, known as Large Hadron Collider (LHC). The collider takes time in range of nanoseconds to create high-energy proton-proton collisions at speeds close to light speed.

Two opposite beams are accelerated in a ring with superconducting magnets and accelerating structures. The temperature of the system is very low (around 271.3 °C) limiting the loss energy and conductivity. For this reason, the accelerator temperature is controlled by distribution system of liquid helium [1].

Groups of physics and engineering collaborate with the main goal to organize overall experiments, from events generation and detection up to the final data analysis. Different detectors interface with the LHC to analyze the particles produced by the collisions. They are organized in a shell-structure and each of them is able to detect a specific range of charged particles. For each detectors, there is an associated experiment. ATLAS (A Toroidal Lhc ApparatuS) and CMS (Compact Muon Solenoid) are the biggest ones because they investigate the large range of physics particles. The first is thought to posses information about experiments happening up to 14 TeV energy. CMS experiment is very useful for Standard Model studying, including Higgs bosons, muons, photons and electrons. Both of these experiments contributed in the discovery of the Higgs Boson particle, in 2012, and are further utilized to investigate other particles that could make up dark matter.

Physics experiments without electronic control doesn't exist. In the years, detectors and search methodology of the particles have been developed with the main target to search for more particles and understand the existing particles more clearly. At the same time, this advancement implied a major attention on the electronic parts, on their efficiency and reliability. These requirements led to replace an electronics based on discrete components with integrated circuits, because of the remarkable advantages. The costs have been drastically reduced although a different number of prototype must be produced before to have optimal performance. CMOS technology allows designing mixed-signal circuits, named ASIC, able to work in different worlds, i.e. digital and analog. A high performance analog part is closer to a dense digital logic with considerable benefits of efficiency for unit of area and driving. Integrating a complete mixed-signal circuit in a die, interface and load managing issues are reduced. The ASIC development depends on scaling down technology. Performance, sizing, resolution and number of components, integrable in the same, area are substantially increased with more work by electronic designers.

#### 1.4.1 State Of The Art MDT AFE

As a result of the proton-proton collision, at center-of-mass energies of up to 14 TeV, some charged and neutral particles are generated. Muons are the most penetrating charged particles emerging from proton–proton collisions. In order to determine the energy and direction of the secondary particles emerging from the collision, readout electronics are utilized.

The actually mounted state-of-the-art MDT readout circuit is realized in a 130nm CMOS technology[24,25,26], and operates from a single 3.3V supply voltage. It performs a charge-to-voltage conversion by a Charge-Sensitive-Preamplifier (CSP). The CSP is followed by a three stage shaper design to implement Bipolar shaping scheme is chosen to avoid deterioration of efficiency due to baseline fluctuations due to high signal rates in MDT chambers (up to 400 kHz/tube). A pre-discriminator is also attached to adjust the analog channel sensitivity ( that is voltage output for an input charge pulse) at the input of discriminator. The analog channel is followed by a Discriminator and WADC (Wilkinson ADC) to perform Analog to Digital conversion. Two modes of operations are provided:

- Time over Threshold (ToT) mode: The length of the Discriminator output corresponds to the time of the input signal above threshold and encodes information about input charge.

- WADC mode: The length of the circuit output corresponds to the charge, contained in a time window of 8-16 ns after threshold crossing which represents an approximate measure of the peak amplitude of the incoming signal.

The channel can be programmed by the external FPGA board, before operating, to operate in wither ToT mode or WADC mode. In ToT mode the rising edge of signal represents the charge arrival time where as the length of the signal gives information the amount of charge being arrived. The Wilkinson ADC (WADC) [26] performs an

approximate measurement of the amplitude, by charging and discharging the holding capacitor, of the incoming signal in the time window shortly after the signal was triggering the discriminator. Knowing this amplitude allows for a correction of the raw trigger time for time slewing and in addition it also provides diagnostics for monitoring the gas gain of the chamber. To suppress multiple threshold crossings for a single track passing a tube, a "dead time" (DT) is introduced, disabling the discriminator for a programmable time after a threshold crossing. The Dead-Time can be selected in the range 150-750 ns.

For a 60pF detector capacitance, classical readout electronics (ASD) features a sensitivity of 8.9mV/fC at the output of Analog chain, 15ns nominal Peaking Time Delay (i.e. PTD, the front-end capability to quickly detect charge arrival time) and low-noise enabling 5fC minimum detected charge at 10dB Signal-to-Noise-Ratio (i.e. SNR).

In the process of renewing the MDT readout electronics, one of the main objectives is to make a significant low-power and area-efficient design using long-term sustainable technology, along with achieving all the functional parameters of MDT-ASD [24,25,26].

This Thesis presents a new readout electronics circuit designed in 65nm CMOS technology, highly optimized in terms of area and power efficiency along with achieving the same performance. The power consuming components are identified and are carefully designed by selecting the right topology and design parameters to minimize the power consumption without deteriorating the performance parameters. The design incorporates a two-stage shaper to implement bipolar shaping of the input signal. This design has a single mode of operation, time over- threshold. The W-ADC mode, used for signal charge measurement and time-slewing corrections in the reference model, has become unnecessary due to the larger gain observed at the unchanged input-referred noise level of the new-generation chips, so it has been eliminated. To avoid bulky capacitors, as used in the three-stage shaper of the previous design, the sizing of passive components has been optimized to minimize RC component sizes, resulting in a 4x area shrinking factor in the shaper stage w.r.t. to the previous design. SLVS drivers have been designed to provide an interface for the FEE system to TDC, which is the subsequent stage of the readout chain.

# 2 Chapter 2: FEE Design Overview

## 2.1 Front End Electronics Design

High-Energy-Physics (HEP) experiments developed in the last decades [27]-[28]-[29]-[30] target to describe the high energy particle interactions.

The main target of High-Luminosity Large-Hadron-Collider (LH-LHC) ATLAS experiments is to search the elementary particle of the Standard Model, studying a broad spectrum of physics processes, and to study physics beyond the Standard Model. For this purpose, it requires a complex detection system as that shown in Figure 10.

According to [33] [34], muons measurement uses two completely independent systems called Inner Tracker and Muon Spectrometer [35]. The Inner Tracker is surrounded by a superconducting coil which generates a magnetic field parallel to the beam axis where there are three different sensor systems. It performs the measurements of direction, momentum and charge of electrically charged particles produced in each proton-proton (p-p) collision. The muons emerging from the primary collision, being the most penetrating charge particle component, are able to transverse the Calorimeters and to reach the Muon spectrometer, the outermost shell of the ATLAS detector. The Muon Spectrometer (MS) surrounds the calorimeters and consists of three large air-core superconducting magnets providing a toroidal field (each with eight coils); a system of precision tracking chambers and fast detectors.

A proper readout electronic circuit is designed for each part to detect and record the useful information. This chapter, presents a read-out front-end, dedicated to the Monitored Drift Tube (MDT) chambers.

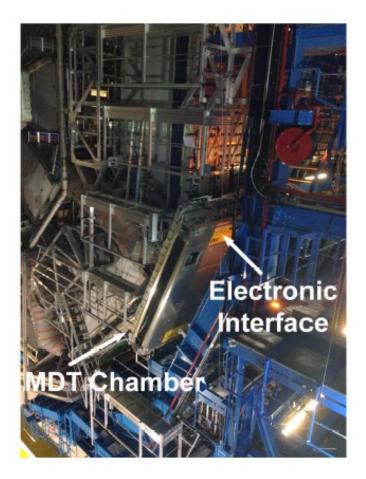

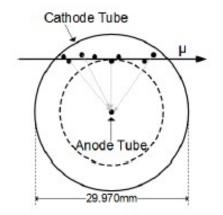

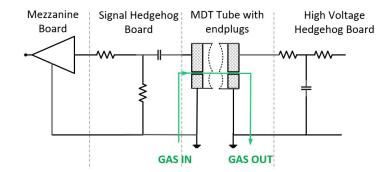

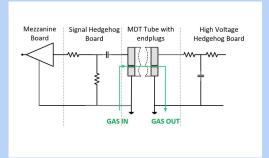

The MDT chambers are the main components of the precision tracking system [32]. The tubes have 29.970mm of diameter and they are organized in six layers arranged [36], a cross section of MDT tube is shown in Figure 11. They are connected to electronics containing the readout electronics as represented in Figure 12. An impedance matching network avoids reflections and losses of charge detected. About that, each wire operates with Ar/CO2 gas (93/7) at 3 bar and it is terminated with the equivalent transmission line impedance of the tube (383). In addition, all contacts between the chamber and the hedgehog board are gold plated to ensure a long-term connectivity.

A section of the MDT tube is reported in figure 12. Electrons generated by muons in the gas-filled pressurized MDT tubes are drifted to the central wire of the tube, where their time-of-arrival is used to determine the distance of the track from the wire (RMIN in Figure 11). The main operating parameters of the MDT are summarized in Table 2.

As the muon usually passes through a large number of drift tubes, the position of the muon track can be reconstructed from a combination of measurements in the tubes along the muon trajectory. The specific details on ATLAS experiment and setup can be found in [36]. Considering a simplified MDT readout scheme (Figure 12), the small charge signals, coming from the wires, are sent to the 'mezzanine board' where the readout circuit is placed. Each 'mezzanine board' contains 24 channels organized in 3 Octal groups and it is connected to a single 24-channel Time-to-Digital Converter (TDC) and to a proper control circuitry [19].

The monolithic readout chip senses, shapes and converts the signal coming from the tubes, providing time-domain voltage pulses, whose duty cycle is proportional

Figure 10: Photo of ATLAS Detection System[2].

Figure 11: Section of MDT tube.

to the amount of charge at the circuit input. The output signal of the discriminator is triggered when the voltage pulse crosses a programable predefined and adjustable threshold, and is subsequently sent to an, off-chip, TDC, which forwards the recorded information to data acquisition chain for recording and track reconstruction. Before moving on to analyze the most important requirements for MDT read-out channel, it is important to point out that the choice of the ionizing gas has been done for its favorable aging properties in the LHC environment [19]. Unfortunately, it is

| Parameter                    | Large Tubes                        | Small Tubes                |

|------------------------------|------------------------------------|----------------------------|

| Length                       | 1.5 to $6$ m                       | $1.5$ to $2.50~\mathrm{m}$ |

| Diameter                     | 30 mm                              | $15 \mathrm{~mm}$          |

| Wire diameter                | 50  um                             | idem                       |

| Wire resistance              | $44 \ \Omega$                      | idem                       |

| Impedance                    | $380 \ \Omega$                     | $340 \ \Omega$             |

| Termination                  | 380 $\Omega$ in series with 470 pF | 340 $\Omega$ with 470 pF   |

| AC coupling                  | 470 pF                             | idem                       |

| Drift gas                    | Ar/CO2 (93%/7%)                    | idem                       |

| Maximum hit rate             | 500  Hz/cm2                        | 30  kHz/cm2                |

| Nominal operating voltage    | 3000 V                             | 2730 V                     |

| Electron avg. drift velocity | 20  m/ns                           | 42  m/ns                   |

| Maximum drift time           | 750 ns                             | 180 ns                     |

Table 2: Operating parameters of MDT chambers with large and small tubes.

Figure 12: Simplified Scheme of Muons Detection system[32].

a non-linear drift gas and from this situation results difficult track reconstruction solving with a programmable dead-time up to the total drift time.

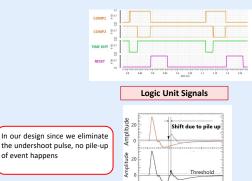

# 2.2 Channel Architecture

The FEE65nm is a four channel CMOS design which has been optimized for the ATLAS MDT chambers. It is an advance version of ASD130nm [24,25] which is an Ultra-Low-power and area efficient design, in a long sustainable technology, with the same performance parameters as the reference design. The efficiency is achieved by optimizing the architecture of every block of its precedent model without effecting the performance parameters. It has a single Mode of operation, Time-Over-Threshold, eliminating W-ADC Mode which performs an approximate measurement of the amplitude of the incoming signal in the time window shortly after the signal was triggering the discriminator. Time-Over-Threshold measurement gives us enough information to know the charge arrival time and the amount of charge being detected as a result of proton-proton collision.

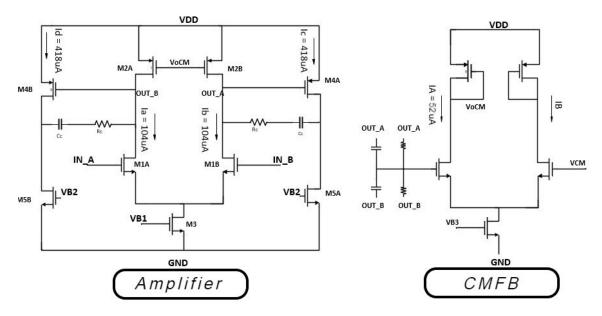

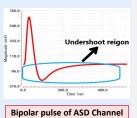

For the CSP, a large bandwidth, single-ended two stage amplifier is used. Since the input signal comes from a single source, the single ended topology is utilized keeping in view its power efficiency benefits as compared to fully differential topology. The three-stage shaper of ASD130nm, utilized to implement the bipolar shaping

scheme, is replaced by a differential two-stage design and the Pre-Discriminator stage is eliminated. The bipolar shaping scheme is implemented to avoid baseline variation error.

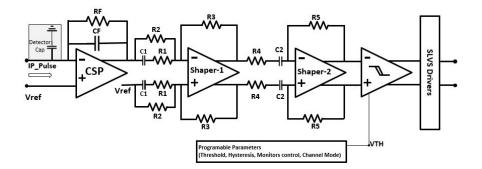

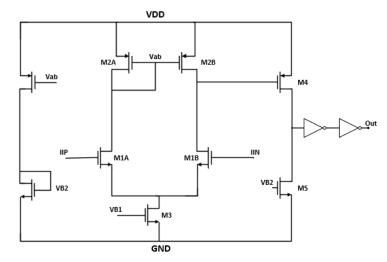

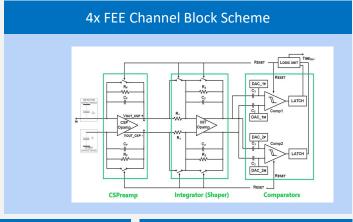

Figure 13: ASD Single Channel Schematic.

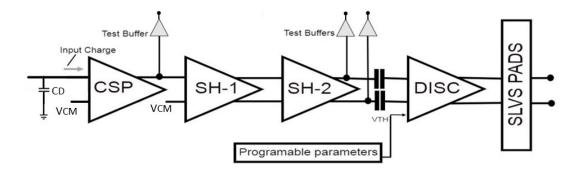

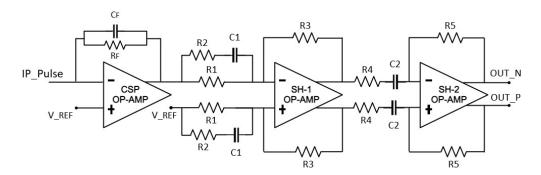

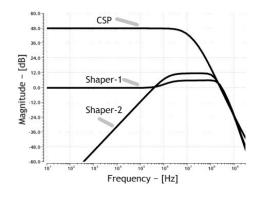

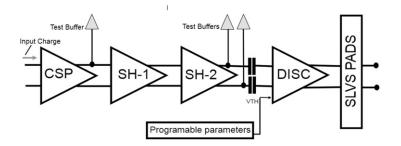

Each channel, as shown in Figure 13, consists of a single ended Charge Sensitive Preamplifier (CSP) and differential two stage shaper (SH1-SH3), to implement bipolar shaping, followed by a discriminator. The discriminator compares the incoming signal to a programable threshold value and output a digital pulse.

The CSP amplifies the input charge, generating an amplified voltage signal which is further amplified and shaped in the Shaper stages. The conversion of Analog chain from single ended to differential, in Analog channel, is for the purpose of Noise immunity and high-power supply rejection ratio while bipolar shaping is selected to reduce the effects of baseline shift at high signal rates [37][38][39]. Negative terminal of CSP is connected to the signal source of the MDT tube (i.e. the central wire), while the positive one is fixed with an internal resistor divider to a proper bias voltage. A capacitor of up to 60pF is attached to negative terminal, assuming the parasitic capacitance.

For each of the four channels, the output of the shaper stage is fed directly into the discriminator stage, unlike the previous design in which the output was fed into pre-discriminator stage and W-ADC. The discriminator stage compares the output of shaper with a programmable threshold (DISC1 threshold). At the moment of threshold crossing, the (digital) outputs of a discriminator change polarity, going from LOW to HIGH, thus defining the "leading edge" of the ASD output. This leading edge corresponds to arrival time of charge. Whereas the width of the Digital output gives a time measurement of the amount of charge being arrived.

For storing and processing the digital content (binary word to program the chip) of design, a novel design is used for shift registers. Unit cells based on parallel arrays of Serial-In-Parallel-Out (SIPO) and Parallel-In-Serial-Out (PISO) blocks are used to confirm the correctness of data loaded to design.

At the output the FEE65nm the output is available as both, low voltage differential signal, with a voltage swing from 200mV to -200mV , and digital CMOS Level signal, with high level as 1.2V and low level with 0V.

## 2.3 Analog Chain

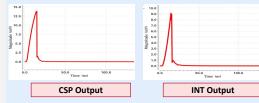

Overall FEE65nm is a mixed signal design, comprising of both Analog and Digital section. The Analog section of the design consists of Preamplifier and two stage Shaper. The negative input of the CSP (Figure-13) is connected to the signal source of the MDT tube, that is, the central wire. The CSP amplifies the input charge, generating a proportional voltage signal which is amplified and shaped in the subsequent stages whereas the two-stage shaper implements the Bipolar shaping.

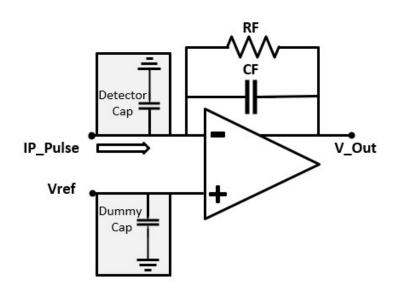

#### 2.3.1 Charge Sensitive Preamplifier

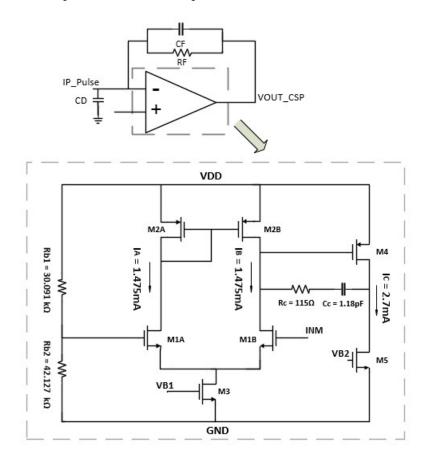

The Charge Sensitive Preamplifier, shown in Figure 14, is the first stage of Analog Chain. It is designed using two-stage amplifier topology as shown in Figure 15. The input signal is attached to the negative terminal of CSP. A capacitor of 60pF, assuming the detector capacitance, is attached to this node. The positive input has been fixed by a resistor divider (Rb1 and Rb2) to 700 mV, generated on chip. To suppress the substrate noise, a capacitor of 16pF is attached to the positive terminal on Board.

Figure 14: Scheme of a Charge Sensitive Preamplifier.

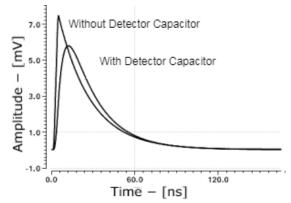

CSP design is very critical as it defines allot of key functional parameters of the system. Performance and functional specifications such as signal rise-time, overall power consumption, noise, is largely defined by this block. Along with the high specification criteria, the performance of this block is adversely affected by very large value of CD, parasitic capacitance, due to the PCB parasitic and the long wires of connection between the ASD and the tubes. This high parasitic capacitance affects the closed-loop-gain bandwidth, sensitivity, and signal rise time of the CSP. Key design parameters for CSP performance are minimum noise generation, minimum power consumption and high rise-time. To achieve these specifications, it is designed with a very high trans-conductance value of 25mA/V for input Mosfets.

This is in accordance to target the design for minimum noise generation. This technique however has a trade-off of an increase in power consumption as high the transconductance is, more is the current it consumes. The currents IA+IB, IC

Figure 15: Scheme of OpAmp used.

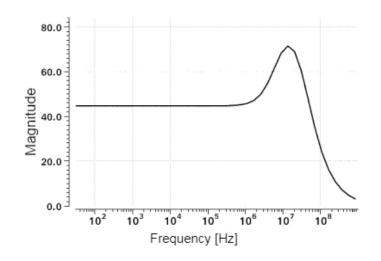

shown in Figure 15, are implemented through a current mirror from a reference current source. To compensate for the excessive power consumption, first very large size mosfets, W/L = 580u/330nm, are used and are operated in sub-threshold region. Along with that, as the input comes from a single source (Anode wire of Tube) a single ended topology is used and hence saving a current of 2.7mA in the outer stage of amplifier and eliminating the use of common-mode feedback circuit, in likemanner. Apart from this, the overall stages in design are reduced to make it an Ultra-Low-Power design. To make the CSP faster, as requirement for high rise-time, the OP-Amp is designed with a very high gain bandwidth 0f 2.4GHz with a phase margin of 60 degree, ensuring good stability of CSP. With these open loop characteristics, the CSP shows a very fast peaking time of 4ns without the detector capacitor and 10.5ns with the large (60pF) detector capacitor. The values of currents, voltages, dimensions of passive/active components are reported in Figure 15 and in Table 3. The load impedance of CSP stage is the input impedance of Shaper-1 and 2. It is, a parallel combination of a Resistor, Rs1 with a series of Resistor and Capacitor, Rs2 and C1 respectively, shown in Figure-13. The CSP transfer function depends on the feedback network (parallel network of RF and CF), the transconductance of the input transistor (M1AB), the output impedance (ZL) and the detector capacitance (CD). It can be approximated by:

$$T(s) = \left(\frac{-R_F(1 - \frac{sC_F}{gm_{M1}})}{(1 + sC_F R_F(1 + \frac{C_D}{C_F} \frac{1}{gm_{M1} Z_L}))}\right)$$

(1)

Similarly, the input impedance transfer function is approximately given by Eq. 2:

$$Zin = \left(\frac{T(s)}{gm_1 Z_L}\right) \tag{2}$$

It is almost constant (ZIN 44 ) at low frequencies and below 63  $\,$  all in-band frequencies.

|     | /                                 |                       |

|-----|-----------------------------------|-----------------------|

| MOS | W/L                               | Gm                    |

| M1A | 580um/330nm                       | $25 \mathrm{mA/V}$    |

| M1B | 580um/330nm                       | $25 \mathrm{mA/V}$    |

| M2A | 340um/200nm                       | $19 \mathrm{mA/V}$    |

| M2A | 340um/200nm                       | $19 \mathrm{mA/V}$    |

| M3  | $180 \mathrm{um}/200 \mathrm{nm}$ | $31.45 \mathrm{mA/V}$ |

| M4  | $600 \mathrm{um}/200 \mathrm{nm}$ | $33 \mathrm{mA/V}$    |

| M5  | $30 \mathrm{um}/200 \mathrm{nm}$  | $27.4 \mathrm{mA/V}$  |

Table 3: CSP W/L and Trans-conductance value.

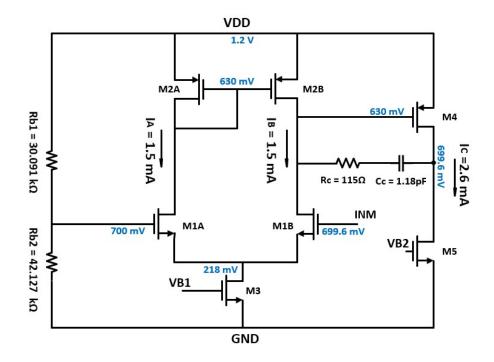

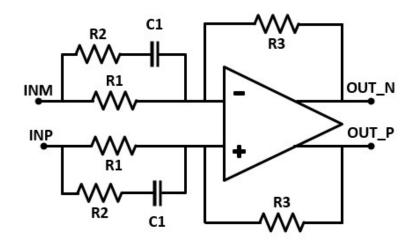

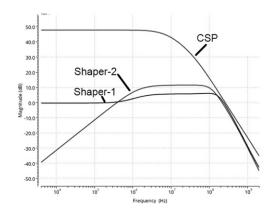

#### 2.3.2 Shaper

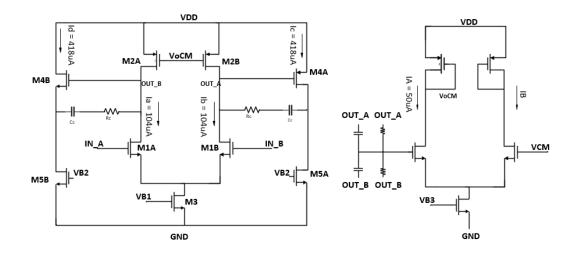

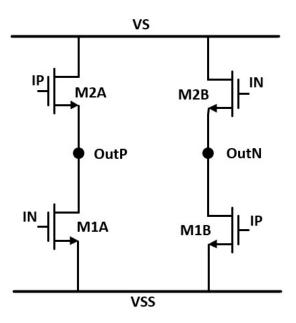

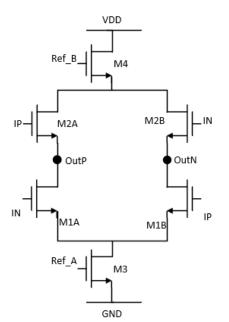

The Preamplifier stage is followed by a two-stage shaper, Figure 16-17, to implement bipolar shaping of pulse, to avoid deterioration of efficiency due to baseline fluctuations. Each stage of shaper is based on two stage fully differential amplifiers as shown in Figure-18.

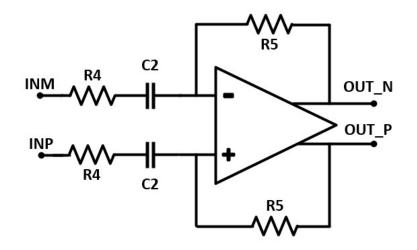

Figure 16: Shaper 1.

The choice of two stage differential topology is due to the reason of being more robust to load and high output swing. Since we are operating from a 1.2V supply now, two stage topology is the best choice to achieve a maximum linear qwing at the output of shaper. The transconductance value of Input mosfets is 2.5mA/V and it consumes a current of 104uA in each of inner stage, Ia Ib, and 418uA in each of outer stage as shown in Figure 18. The Outer stage mosfets are designed with an overdrive voltage of less than 100mV to have the maximum linear sensitivity, for full range of input charge up to 100fC. To set the common mode feedback voltage a separate common-mode-feedback CMFB network is designed whose W/L value is half as that of main amplifier input stage, to save current consumption. The CMFB network is attached to main amplifier through a common-mode level sensing network, consisting

Figure 17: Shaper 2.

Figure 18: Scheme of OpAmp used.

of a pair of resistors with capacitor in parallel for better performance at higher frequency.

Each stage of the shaper (shaper 1–2) has an input impedance network and a resistive feedback loop, as shown in Figure [16,17]. The poles and zeroes used to implement the bipolar shaping are the same as in ASD130 [24,25,26], selected to cancel the very long time constant component of the positive ion MDT pulse, however, the values Z-RC are greatly changed, shrunk by almost a factor of four, with the aim of an area-efficient design. The values of impedance network components are given in Table 4.

The transfer function of each shaper stage depends on the input impedance and feedback network. Equations (3) and (4) show the transfer function of shaper-1 and shaper-2, respectively.

$$T(s) = \frac{R3}{R1} \left( \frac{1 + sC_1(R_1 + R_2)}{1 + sC_1R_2} \right)$$

(3)

$$T(s) = \left(\frac{sC_2R_5}{1+sC_2R_4}\right) \tag{4}$$

| Stage    | Component     | Value                  |

|----------|---------------|------------------------|

| Shaper-1 | R1            | $9.8 \text{ k}\Omega$  |

| Shaper-1 | C1            | 10.2  pF               |

| Shaper-1 | R2            | $10.1 \text{ k}\Omega$ |

| Shaper-1 | $\mathbf{R3}$ | 9.8 k $\Omega$         |

| Shaper-2 | $\mathbf{R4}$ | $9.8~\mathrm{k}\Omega$ |

| Shaper-2 | C2            | 11.5  pF               |

| Shaper-2 | R5            | 37.8 k $\Omega$        |

Table 4: Shaper Impedance Network components value.

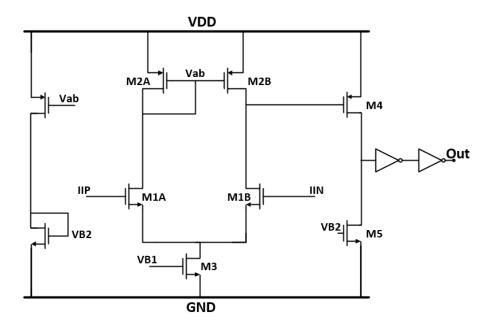

#### 2.3.3 Discriminator

The Bipolar output signal of Analog Chain is passed into comparator stage where it is compared with a threshold value. Coupling capacitors are utilized to separate the discriminator from the Analog section

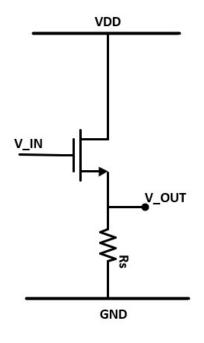

The comparator is designed using two stage single ended amplifier topology, without compensation as shown in Figure 19. It is a high gain amplification stage, followed by a series of inverters to give the output as High or Low depending on input signal and threshold value.

Transient noise is always present in CMOS design and causes fluctuation when it comes to threshold crossing. For this reason a Hysteresis Block is added to comparator to unbalance the current in main differential amplifier by a programmable value. Its significance is to remove glitches in the output of comparator because of noise. The hysteresis can be varied from 0 - 50mV using 3-bit programmable code and can be set into eight different values in range of 0-50 mV.

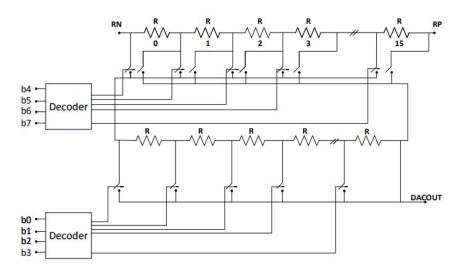

The Threshold value for main comparator is set deferentially, i.e varying the baseline voltage at both terminals of comparator by same amount, across the baseline voltage of the channel. Two sets of 8-Bit string DAC and 3-To-8 bit Decoders are used to set the threshold values which are programable up to 256mV across the common mode voltage with LSB of 2mV. String DAC is a collection of resistors in series, acting as voltage divider circuit, with switching points or tap nodes between each of the resistors. Each string-DAC is composed of main string and sub-string to divide the reference voltage and give output voltage with LSB of 1mV. Complementary switches are designed for selecting required output voltage to set threshold value.

### 2.3.4 SLVS Driver

Modern experiments in high-energy physics contain a huge number of data processing events in channels. Therefore, reducing power consumption and increasing data transmission speed of each individual front-end ASIC is an important task.

The front-end electronics aim to achieve high levels of performance in terms of resolution and accuracy. This performance is limited by the system intrinsic noise,

Figure 19: Scheme of OpAmp used.

Figure 20: String DAC and Decoder.

therefore electrical links should be designed to minimize cross-talk and power supply noise. For these reasons, using a low-power, low-voltage-swing signaling standards become a very popular in particle physics applications in recent years.

Since a low-power, low-voltage-swing signaling standards is very important in particle physics, for these reasons along with CMOS level signal at output for testing purpose, SLVS driver is designed. The SLVS standard is defined in [40] and describes a differential current-steering electrical protocol with a voltage swing of 200 mV on a 100 load and a common mode of 200 mV. The differential voltage is therefore 400 mV. The output current is 2 mA, with a power consumption at the load of 0.4 mW.

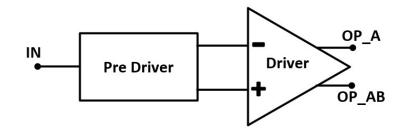

Block diagram of SLVS driver is presented in Figure-21, this is composed of a

Figure 21: SLVS Block Diagram.

Figure 22: SLVS Transistor Schematic.

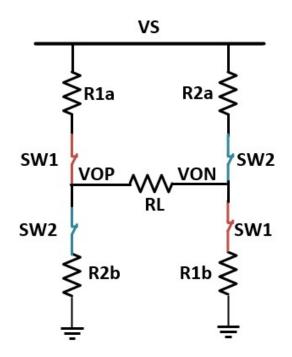

pre-driver and a transmitter (Tx). The pre-driver takes the input from the comparator and convert it into differential signals with opposite phase. A typical SLVS transmitter operates as a current source with switched polarity [41,42]. The output current flows through the load resistance, external to chip, establishing the correct differential output voltage swing. The proposed transmitter circuit, presented in Figure-22, uses the configuration with four MOS switches in H-Bridge configuration, implemented with the M1-M2(AB) NMOS transistors. The operation of this circuit is described in the following. When M1A and M2B transistors are switched on, the polarity of the output current is positive together with the differential output voltage. On the contrary, when M1B and M2A transistors are switched off, the polarity of the output current and voltage is reversed.

## 2.4 Programmable Functional Parameters

For proper functioning of FEE65nm chip, some functional parameters can be setup or vary in pre-run time. It includes threshold voltage, hysteresis control, channel mode control. A 55-bit digital word is transmitted to the chip using a simplified JTAG protocol, serial interface, based on a chain of register, transmits the word code to its target block in the chip. Table 5 gives a summary of the Programmable parameters together with the number of bits, corresponding range, and resolution/LSB. Programmable parameters manage channel/chip operation and functioning.

| Parameter       | Range       | Unit |  |  |

|-----------------|-------------|------|--|--|

| Disc Threshold  | -255 to 255 | mv   |  |  |

| Disc Hysteresis | 0 - 50      | mV   |  |  |

| Dead Time       | 50 - 500    | ns   |  |  |

| Channel Mode    | HI, ON, LOW |      |  |  |

Table 5: Programable Parameter of FEE Chip.

#### Discriminator control:

The Discriminator Stage compares the output of Analog Section with a threshold voltage (VTH) and uses a hysteresis to avoid multiple threshold crossings due to noise.

VTH is applied at the AC coupled input of the Discriminator stage and is generated by two complementary 8-bit String resistor DACs. By setting the reference voltage, two mirror voltages are generated across the common mode voltage to establish the threshold voltage. The final differential output threshold can vary from -255 mV to +255 mV with an LSB of 2 mV.

#### Hysteresis control:

It was demonstrated that the option of a wide-range adjustable hysteresis for the timing discriminator is a useful feature to reduce the probability of multiple threshold crossings in the tail of the MDT signal[37,38].

It also improves the system reliability by removing ambivalent output states of the comparator due to signals or signal fluctuations close to the threshold level. Hysteresis is applied through a scaled-transistor current source with a resolution of 3 bits. The range of the hysteresis is 0 - 50mV variation.

#### Channel Mode:

For diagnostic purpose, to check if the channel is working or no, it is be useful to force the SLVS output to a logic HIGH or LOW. One of the following channel operation modes can be selected:

- ON MODE: default working setting; the output depends on input signal;.

- HI MODE: the output is forced to HIGH or 'Logic 1'.

- LO MODE: the output is forced to LOW or 'Logic 0'.

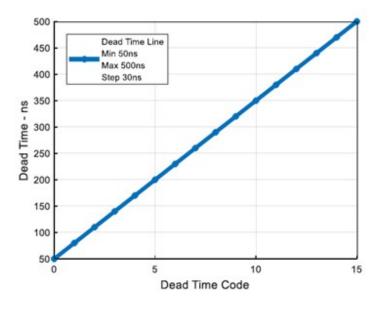

#### Dead Time:

Dead Time is the time interval in which any threshold crossing of discriminator will not produce any output. It is the time between the leading edge of one output to the leading edge of consecutive next output.

This feature of the chip allows to suppress multiple threshold crossings. This time interval is controlled by a 4-bit digital code. DT circuit is made up of a series of RC Delay elements with controlled switches, thus able to produce configurable deadtime interval once activated by the edge of TOT output. Selectable range of deadtime is from 50ns to 500ns in steps of 30ns. Figure-20 presents the response of dead time vs. 4-bit code.

The deadtime window is added to the output pulse, thus a minimum deadtime is always present (the time of the output pulse itself).

Figure 23: Dead Time VS Dead Time code

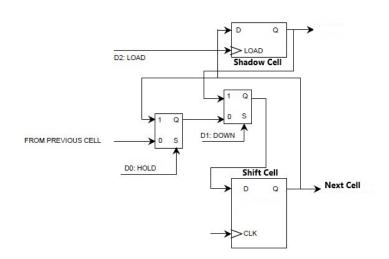

## 2.5 Serial data I/O and programmable parameters

It was found advantageous to be able to control or tune certain analog and functional parameters of the MDT-ASD, both at power-up/reset and during run time. Rather than applying external currents or voltages, it was chosen to send the control signals as digital data to the chip, where they are converted into physical quantities by custom Digital-to-Analog Converters (DACs) as required. A serial I/O data interface was implemented in the circuit, containing digital I/O ports, shift registers and the required control logic. The data as well as the control signals and the shift register clock are generated by an FPGA off the chip and are transmitted to the chip using a JTAG like protocol.

**ASD serial data interface** The selected FEE serial data interface architecture utilizes separate shift and working registers. The shift register is connected directly to digital input and output pads respectively. Its length is designed to hold a complete set of control bits (55). The data can be uploaded any time to the

shadow registers, which control the DACs, multiplexers etc. The architecture allows downloading the whole set of active bits from the shadow to the shift register in order to send them back to the controller for diagnostic or monitoring purposes. This can be done any time and does not interfere with the normal operation of the chip.

The interface, for each data bit, consists of the shift register-cell, implemented as a static master-slave D flip flop. And a shadow register cell, realized as a static transparent latch and also 2 two-in-one multiplexers as shown in Figure 24.

The protocol requires 2 data lines (TO and FROM chip), 3 control lines (LOAD, HOLD, DOWN) and one clock line as shown in Table 6. The configuration allows extensive control over the data flow.

Figure 24: Serial Data Interface

- HOLD mode keeps the data in the shift register by feeding back each cell with its own content.

- SHIFT mode shifts data right at the rising edge of the clock. LOAD active copies the bits in the shift register to the shadow register at any time (asynchronous).

- DOWN active copies the contents of the shadow registers to the shift register at the next rising clock edge (overrides SHIFT HOLD).

The FEE serial input expects the data to be stable at the rising edge of the clock. The circuit will change data bits at the falling clock-edge. Thus data are stable at the input for the entire clock period with the sensitive rising edge in the middle. Data bits at the ASD serial data output also change state at the falling edge of the clock. Shift and shadow registers have a length of 55 bits, where 54 are actual data bits. The last shift register cell is clocked with an inverted clock, making the output change at the falling edge of the clock. A DOWN instruction causes the last cell to perform a HOLD operation.

| Table 0. Berlai interface signal lines. |                                                        |  |  |

|-----------------------------------------|--------------------------------------------------------|--|--|

| Parameter                               | Function                                               |  |  |

| DATA IN                                 | Data line from controller to ASD shift register input  |  |  |

| DATA OUT                                | Data line from ASD shift register output to controller |  |  |

| CLK                                     | Clock line                                             |  |  |

| D[0:2]                                  | Register control lines                                 |  |  |

Table 6: Serial interface signal lines.

| Table 7: Serial interface instruction end | coding. |

|-------------------------------------------|---------|

|-------------------------------------------|---------|

| Instruction | Do | D1 | D2 | Operation                                    |

|-------------|----|----|----|----------------------------------------------|

| SHIFT       | 0  | 0  | Х  | Shift right at rising edge of CLK            |

| HOLD        | 1  | 0  | Х  | Keep shift register contents (self feedback) |

| DOWN        | Х  | 1  | Х  | Copy to shift register @ rising edge of CLK  |

| LOAD        | Х  | Х  | 1  | Load shadow registers @ rising edge of CLK   |

## 2.6 Front End Electronics Design- V2

Although in the measurements, shown in chapter 5, promising results have been reported as compared to simulation results, however, following the chip testing two modifications were proposed for the FEE-V2:

- Improving response-time of SLVS Pads

- Test point monitors at output of CSP and Shaper

The response time of SLVS drivers as shown in simulations, is slow, have a rise time of 10ns. The phenomena is even further deteriorated in measurements due to parasitic effects. Along with that, adding test point monitor buffers at output of CSP and Shaper can provide a window to inside the channel to visualize the signal in different stages of the channel.

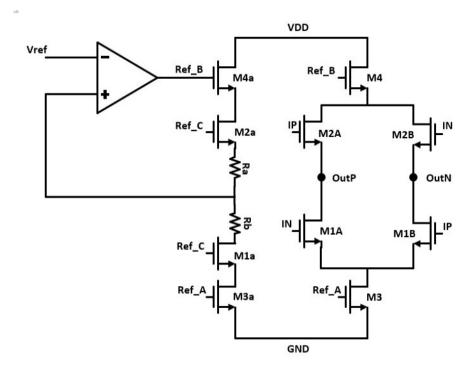

### 2.6.1 New SLVS Design

The basic principle of a new SLVS driver [43] are explained with the help of idealized model as shown in Figure. It consists of four devices that can be represented by by resistor-switch pairs. At a time, either the pair of branches containing R1a and R1b resistors or the pair of branches containing R2a and R2b resistors is connected through the switches to the load resistance RL. The RL resistance is off-chip and is equal to 100, while the other four resistances should be equal to 50.

With such a circuit configuration, the the VON node potential is equal to 1/4VS, while the VOP node potential is equal to 3/4VS, which results in  $\pm 1/2VS$  voltage swing across RL resistance. The value of VS=400mV, so it results in swing is equal to  $\pm 200$ mV. The resulting eye diagram for the described case is shown in Figure 2.

The resistors in ideal model mentioned above, are replaced with NMOS as shown in Figure. With appropriate in put voltages (IN-IP) the mosfets are turned ON or OFF to make the circuit work as explained for idealized.

Figure 25: SLVS Block Diagram

Figure 26: SLVS Schemaitc

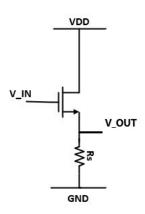

#### 2.6.2 Test Point Monitors

Test Point Monitors are designed to visualise the signal inside the Analog chain. They are connected at the output of CSP and Shaper and are connected only in channel four.

The Monitors are based on common drain topology topology with a load resistance equal to 800 ohms as shown in Figure. The amplifiers shows a gain of 0.75, lower sensitivity then the actual is observed at output, but since it is only for signal monitoring purpose so a gain lower then unity does not make any difference. When the test point monitors are connected, the sensitivity of that particular channel is decreased due to loading effect of the buffer. For this purpose cmos switches are connected that can turn off the monitor-buffers when not in used. The switches are controlled by digital signal programmed from external board.

Figure 27: Test Point Buffer

## 3 Chapter 3: Design Layout

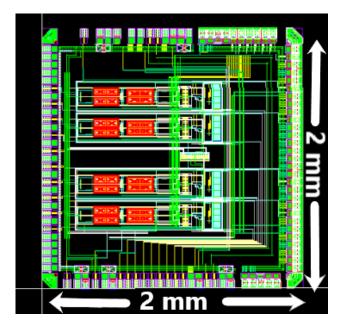

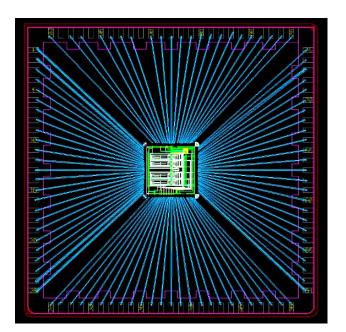

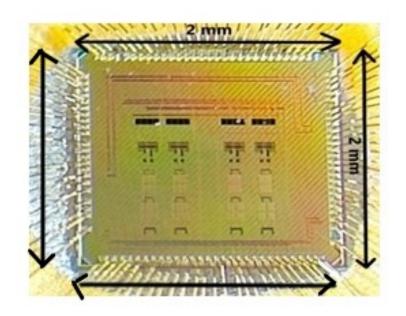

This section is dedicated to the layout of four channel front-end-electronic design. The layout is the final design step after which it is send for chip fabrication. Schematic designed is translated in a drawing form using metal layers provided from foundry to realize the chip.

The layout design consists of following blocks:

- a Pad-ring (with 100 pads, cover area of 2mm\*2mm)

- Four Channels Front-End-Electronics design (with single channel area of about  $0.4 \text{ mm}^2$ )

- a Common Bias Block

- Two array of SIPO, PISO memory unit cells

## Channel Layout:

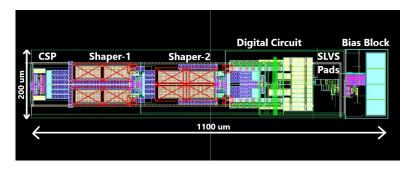

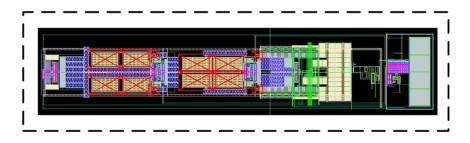

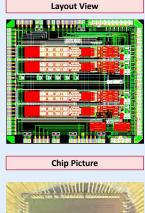

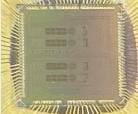

The layout design of every block, CSP, Shaper etc, is done separately, first, and its performance is tested through post-layout simulations. By connecting the independent blocks layout, the channel layout is completed as shown in Figure 28. Each channel, shown in Figure 28, occupies an area of 0.235 mm<sup>2</sup>.

Figure 28: Channel Layout.

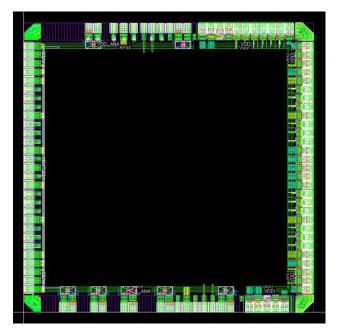

## Pad-ring Layout:

The four channels, which are similar design, are placed symmetrically in the padring. The pad-ring consists of 100 I/O pads which cover an area of 2mm by 2mm. The pads provide a connection to the off-chip world. Pad circuits are defined by the foundry which includes a bond-pad contact and diodes for protection, for the reason to avoid on-chip circuit damage due to external electrical discharges, etc.

The pad-ring includes pads for analog signals, digital signals and power signals. The pads for analog signal are placed at left side and bottom-left of the chip from where the input signal is inserted into the chip and the analog output of SLVS drivers is connected, respectively. The input charge pulses are generated off-chip and are connected to input pads, eight pads, placed on left side of the chip. The eight pads for SLVS driver output are placed at bottom of the pad ring. For uniform power distribution, different power and ground pads are distributed on four sides of the chip. The digital Pads are placed on right and top-right of the chip, where the

output signal of discriminator is connected and the JTAG signals are connected, respectively. Figure 29 shows the pad-ring diagram.

Finally, as regards supplies/grounds, they are divided to separate analog and digital worlds. In particular, there are:

- Analog supply AVDD and analog groung AVSS

- Digital supply VDD! and Digital groung VSS!

The analog and digital supplies are kept separate on chip to minimize the noise due to digital circuitry as in CMOS design the digital circuits are more noise due to level fluctuation. The AVDD and VDD! are connected to different external power supplies, externally, however the analog and digital grounds are connected on-board.

Figure 29: Pad Ring.

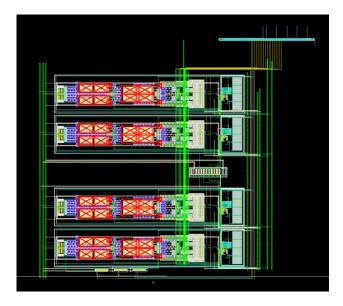

## Core Layout:

The Core layout includes the entire four channel, bias block, memory unit cells of FEE chip except the Pad-ring shown in Figure 30  $\,$